唵嘛呢叭咪吽!在全芯片实现之前清理空头

詹姆斯·帕里斯和阿门·阿萨特瑞恩著

实现过程中的自动短检查可以让设计团队在全芯片验证之前快速发现并修复这些错误,加快了生产时间。

同时进行多个设计元素的设计实现会让你觉得自己是一个魔术师,试图让10个盘子同时旋转!对于正在开发的物理知识产权(IP)块,您应该拥有库交换格式(LEF)抽象表示,因此您可以在芯片级上下环境中验证物理IP数据。但是由于所有事情都同时发生,所以抽象大小、引脚位置或边界大小发生变化是很正常的。您可能会得到与IP数据不匹配的LEF宏。为什么这是个问题呢?

在物理设计实现的这些早期阶段发现的错误可能需要在宏级、芯片级或两者上进行更改。抽象宏和物理IP块之间的数据不匹配可能会产生大量的错误计数,并掩盖根本原因,这意味着您将不得不投入大量的时间和精力来跟踪和修复所有这些错误。你能听到你的时间表碎成碎片吗?

这种系统设计问题的根本原因是在芯片、块或大面积上产生许多违规,通常可以归因于单个或多个相关的布局问题,这些问题会影响布局的基本完整性。电源/地面短路就是一个常见的例子。在片上系统(SoC)平面图中放置一个比该块的抽象占用面积更大的IP块将产生许多短路,这都是由于一个错误。

现在,当然,综合布局与原理图(LVS)短检查将发现所有这些短检查,但这种方法并不适用于设计完整性检查流程,因为它发生在SoC设计与IP块合并之后。如果发现任何短路,则必须修复它们并重新合并数据,这将为流增加额外的开销和时间。

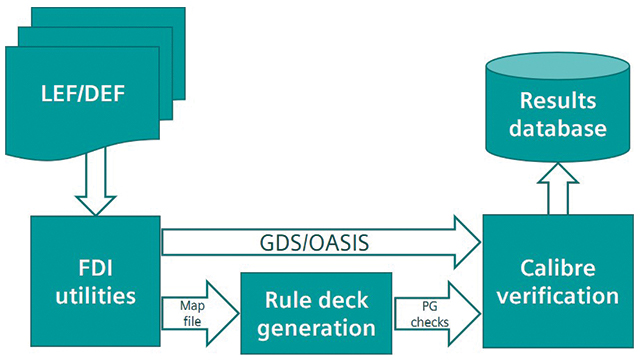

相反,在设计实施过程中,可以使用地点和线路(P&R)过程中使用的相同设计交换格式(DEF)和LEF数据,进行电源/接地短路设计完整性检查。这些LEF/DEF数据文件定义了原始P&R设计中的抽象宏、引脚、过孔、路由和其他对象(如填充)。Calibre平台包含外部数据库接口(FDI)实用程序,可将LEF/DEF数据库转换为GDSII或OASIS格式,将电力/地网数据映射到单独的层,然后生成规则甲板,以自动检查电力和地网之间的直接和间接交互。最重要的是,你不需要成为一个魔术师来实现它。

想知道细节吗?下载一份我们的技术论文,电源/接地短路的早期检测可以加快输出时间,并开始向后调整你的磁带时间表。在我们这个行业,这是真正的魔力!