你所做的任何事情都可以高效地完成。无论是开车(每加仑英里数?),玩体育运动(结果/能量消耗?),还是遛狗(谁拉谁?),你可以高效,也可以不高效。显然,效率越高越好——假设你在乎(有时花精力担心效率可能是低效的)。那么,如果你能发现一项你所关心的活动的改进,它本身就能使你的效率提高近50%,那会怎么样呢?

这就是自旋转移技术(STT)声称他们的新进动自旋电流(PSC)的想法。是啊,这可不是你平常的日常活动。在我们看这些数字之前,让我们先回顾一下相关背景。我们将在这里回顾一些基础知识,尽管我们对MRAM做了更彻底的入门很多年前,我们讨论了STT(公司,不是“自旋转矩传递”技术)最近(但这还是几年前的事了)。

简单地说,MRAM单元由两个由隧道层分隔的磁层组成。其中一层称为参考层,其极性是固定的。另一种是“自由”的,这意味着它的极性可以切换。然后,该单元记录一个1或0,这取决于两个磁层是平行的(即,都有N和S在同一方向)还是反平行的(它们在相反的方向)。每个状态下可以通过隧道的电流量是不同的,这就提供了一种读取状态的方法。

这样的单元格可以以不同的方式使用。一些公司(如STT)生产的MRAM电池被设计成嵌入soc;其他公司(如Everspin)则生产专用的MRAM芯片,与闪存竞争。而且,正如我们将看到的,预期的应用程序也可以驱动细胞如何执行的方向。

更高效的细胞

有一个与开关操作相关的效率,STT将其定义为热障Δ除以诱导开关所需的电流。所以Δ越高,效率越高。编程状态所需的电流越高,效率越低。

这里的关键是热障,有效的开关障碍,它可以防止状态降级,直接影响数据保留。通过添加这个新的PSC结构,屏障提高了,效率提高了44%。这提供了两个机会:一方面,更高的屏障提高了数据保留率——提高了2-4个数量级。或者,如果你通过降低开关电流来补偿更高的Δ,你就会得到与以前相同的整体效率,只是现在使用更少的电流来设置电池的状态。

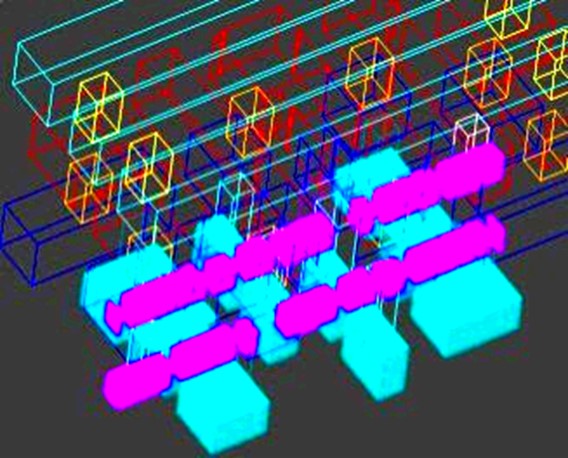

(图片由STT提供)

如果数据保留是您的目标,那么他们说这会将数据保留从几秒增加到几个月。这让我很犹豫:我一直认为MRAM是一种非易失性存储器,但如果你可以在几秒钟内失去你的状态,嗯,这似乎相当易失性。我们一会儿再来讨论这个问题。

他们还发现,这有助于温度性能:对于恒定的Δ,设备会表现得好像温度降低了40度。他们从数据保留测量中获得Δ值,100度时的Δ对应于超过一天的数据保留。

坚持这样的想法

同样,与闪存的10年相比,它的数据保存时间短得惊人。MRAM怎么会是非易失性存储器(NVM),保留时间这么短?

事实证明,这取决于你用MRAM做什么。存储器世界有两大鸿沟:DRAM和SRAM之间的鸿沟和DRAM和闪存之间的鸿沟(所谓的存储级存储器)。这取决于你想用它来弥补哪个缺口。随着时间的推移,我听说MRAM的竞争既基于它的非波动性——与闪存竞争,也基于它的速度、低功耗和易用性,这表明它可能与SRAM竞争。

事实证明,如果你想与闪存竞争,MRAM单元可以设计成长期留存。但是如果你想要一个超小的电池,那么你可以有比SRAM电池更便宜的东西,使用更少的电流(而且没有静态电流)。SRAM没有既定的数据保留要求;假设它是易挥发的,所以它不可能一直停留在架子上。

但是数据保留作为一项规范是专门关注这一点的:芯片断电、闲置或处于待机状态。还有一个问题是在通电时保持状态。DRAM当然不能。部分原因是电荷从电池中漏出,但也因为读取机制是破坏性的。每个读操作实际上都是一个读-还原操作。

MRAM没有破坏性的读取操作,因此它的数据丢失将更类似于泄漏。但是,即使它可能比SRAM消耗更少的能量,如果它一直处于通电状态,而你需要数据保持数小时或数天或其他时间,那么以秒或天为单位的数据保留就有点可怕了。

当然,如果PSC技术能够将用户留存率从几秒钟提高到几个月,那么这便是一个巨大的进步。但是……是的,没有SRAM保留规范,但是人们期望SRAM单元的数据保留是无限的,只要电源一直开着。一个上电的SRAM单元应该永远不会失去状态,除了单事件中断(seu)等。在我看来,几乎没有规格说明,因为任何人都没有想到可能会需要规格说明。

所以,在我看来,降低这种期望可能是一件大事。有几种方法可以解决这个问题。如果他们能够权衡细胞大小,那么他们便能够在更昂贵的版本中提高用户留存率。也就是说,如果他们与6T(或8T) SRAM电池竞争,那么他们有很大的增长空间,而且仍然更便宜。当我与他们交谈时,他们提出了另一种可能性:如果应用程序无法处理额定留存率,那么添加刷新功能将是简单且廉价的。

现在,我不知道你们怎么想,但我认为DRAM刷新是一项极其复杂的业务——它被抽象了出来,所以我们不必担心它。看来,在MRAM芯片中添加这一功能将是一件大事。但STT表示,这将比DRAM刷新更直接、更简单——特别是如果它只需要一天一次刷新的话。

所以,根据STT,这个留存问题,如果它是一个问题,可以变成一个不存在的问题。

略高的堆栈

考虑到PSC的好处,那么它是什么呢?嗯,我们还不能肯定。我们所知道的是,它为MRAM单元堆栈增加了三层。这些层是由什么构成的?这是个秘密。下图显示了它在堆栈中的位置。*你会注意到这就是他们所说的“模块化”:它只是添加到现有的堆栈-无论堆栈可能是什么,除了已经用于制作MRAM的材料或工具外,不使用任何材料或工具。它使晶圆成本增加了大约1美元——几乎是在噪音中。

(图片由STT提供)

也就是说,他们可以把这个添加到任何人的堆栈中,这将会有所帮助。他们还表示,通过重新设计的堆栈(即非模块化的堆栈),他们可能会得到更好的结果。但是模块化也有好处——包括可能获得已经制造mram的代工厂和内存idm的许可。

事实上,这样的讨论正在进行中,增加了他们可能许可的IP列表——包括基本的单元结构以及他们如何做一个3D多级单元。

需要明确的是,根据STT的说法,这背后的物理原理并不是业界一直在研究的东西,STT已经取得了初步成果。他们说他们发明了这项技术——这就是为什么他们对它如此害羞的原因。他们只会说PSC结构与自由层有电和磁耦合。接下来你要发挥你的想象力了。

至于他们的计划,他们预计客户验证将在今年下半年完成,并在2019年投入商业使用。

*“MTJ”是磁隧道结-有效地,标准的MRAM单元。

更多信息:

你如何看待STT取代SRAM的MRAM方法?