多年来,我们幸福地过着各自独立的生活。集成电路设计师?有人无法从你的平板上发送信号?“不关我的事。”包装设计师吗?某个特定信号的电信号很模糊吗?“不关我的事。”印刷电路板设计师?有人不喜欢输出上的驱动器不够高来驱动信号?“不关我的事。” It’s so much easier when you have a restricted scope, and anything outside that scope is someone else’s problem.

但是,如果你真的想优化你的芯片、芯片封装和封装将要安装的PCB(或模块板)之间的交互作用,那么这将不会很好地向前发展。而且,随着我们继续提高集成度和降低尺寸,芯片、封装和板或基板之间的界限开始模糊。

信号可以从晶体管的输出开始,但从那里它通过一系列的触点,通孔和金属痕迹到一个衬垫,在那里它跳上铝线(也许),并循环到线框或其他再分配层,在那里它通过一个球或凸点移动到PCB痕迹一段距离,直到它到达目的地。尽管有所有的域交叉,它仍然是一个信号。

当然,这意味着任何地方的任何问题现在都变成了每个人的问题。如果设计工具在芯片、封装和电路板边缘也失去了硬边界,这可能会更容易。

这里的重点是高级包装和模块,Mentor将这一类别称为高密度高级包装(HDAP)。这种包装有很多变体;Mentor包括FOWLP(一分钟内了解更多)、基于2.5 d中间体的解决方案、CoWoS(一分钟内了解更多)、高引脚倒装芯片和系统级封装(SiP)。

动机包括集成和成本。整合是显而易见的,但成本呢?这样做的好处之一是,你可以把一组不同的骰子放在一起——模拟、III/V材料、数字CMOS、内存——而不需要花费高昂的成本去尝试使用所有这些技术的单芯片解决方案。如果处理得当,你最终会得到一个包含所有东西的单一包,就好像它是一个整体,但它包含多个骰子——甚至“dielets/chiplets”和被动。

是啊,节食或小花冠的概念对我来说很新鲜。这是我从Cadence听到的一个术语,指的是只使用完整芯片的一部分的芯片——比如单个IP块。几乎就像“芯片”现在已经被提升为“soc级”,如果你的芯片还没有达到这个水平——就像十年前所有的芯片一样(想象一下整个芯片只是一个mux!)——那么它就是这些特殊情况中的一种。当然,与过去不同的是,这次我们没有单独包装芯片。

凯蒂丝描述了一个令人惊讶的新方面。我习惯了芯片制造商制造一个芯片,将其包装起来,然后或多或少地将其出售给任何想要将其用于任何电路板或模块的人。现在,很明显,芯片和小芯片被专门设计为集成在一个模块中。这些骰子不会被其他人购买;只有完成的模块才会出售。

你是粉丝吗?

在我们进一步讨论之前,老实说,我对两个更新的打包术语——扇入和扇出——的确切含义感到困惑,与Cadence (DAC之前)和Mentor (DAC)的对话有所帮助。

在解释之后(当然,这意味着一点都不直观——特别是如果你习惯了数字逻辑中这些术语的含义),它有点直观。扇入晶圆级封装(FIWLP或FI-WLP)通常被称为芯片级晶圆级封装(CSWLP)。它指的是一种情况,即再分配层(RDL)将模具信号路由到模具中心,进入少量的球,用于安装在板或其他基板上。它被称为“扇入”,因为外围信号是向内路由的。

扇出晶圆级封装(FOWLP或FO-WLP)是指在FOWLP中被限制在芯片尺寸的衬底比芯片更大,并且可能附加其他芯片或被动式。你可以容纳更多的信号,它们从芯片中被路由出去——或多或少像PCB布局一直以来的方式。因此“扇出。”

这里还有另一个FLA(五个字母的缩写词):CoWoS。这是台积电的一项技术,可以让你把一个芯片放在另一个芯片上(这是晶圆尚未切丁的一部分),然后将这个组合安装到基板上。相比之下,FIWLP(或CSWLP)和FOWLP是通用的行业术语。(我忍不住想把FOWLP读成“foul-up”……或者“fowl-up”,这是猎鸭人看到鸭子飞起来时的叫声,对吧?)

(图片由Cadence提供;我添加了红色矩形来突出模具边界)

(图片由Cadence提供;我添加了红色矩形来突出模具边界)

打包模拟模块

有了这个简单的开场白,我们来宣布一些具体的消息。首先,我们关注模拟。对这个的需求是很简单的,真的。假装一根电线将退出一个模具,通过一个包,并出现在PC板上进行进一步的路由-并将在任何这些边界上有一个漂亮的干净的断裂是幻想。也许它曾经工作过,但是,正如我们上面看到的,我们不需要把它看作是三根电线——在模具上,在封装中,在板上——而是一个单一的连接。任何地方的寄生虫都会影响到任何地方。

当你想到模拟时,许多设计师会想到Cadence的Virtuoso。对于这个主题,他们发布了Virtuoso系统设计平台。它打破了芯片和电路板设计之间的障碍,使它们可以整体地完成。

所有的连接性、模型和库都是自动管理的。它们有一种自顶向下的实现方法,将所有不同的部分组合在一起,还有一种自底向上的方法,专注于分析。数字芯片也可以通过开放获取或通过导入您可能通过第三方获得的任何其他完整的芯片来添加。甚至可以包括离散,因为许多供应商将提供一个设备模型映射文件。然后,您将获得模块的物理占用和示意图模型。

完成后,您将运行布局与原理图检查。大部分自动生成的基本布局都是正确的,但Cadence说还有其他方面需要检查。

FR-4和硅竞争

在一个单独的公告, Mentor在他们的Xpedition工具上引入了几个用于管理HDAP实现的变体。

随着对更紧凑路由的需求的增长,您开始超出传统FR-4(或其他有机)板的可能范围。与此同时,硅正在管理10纳米级的芯片。这种尺寸级别需要大量昂贵的晶圆制造设备,但通过在硅上打印线条,可以比有机材料做得更好——大约2或3毫米,而不是8或10毫米。

不像模具,你先沉积铝(或铜),然后蚀刻掉多余的部分,这是一个添加过程,你可以把金属“放置”在你想要的地方。你不能像在晶圆上那样有侵略性的音调,但它的制造成本要低得多。

Mentor列出了有机板和硅之间的几个不同之处。这意味着要么期望必须改变,要么需要工具来弥合期望之间的差距。

(来源:导师)

第一个Xpedition变体叫做Xpedition基板积分器;它是为建筑师和芯片设计师使用的,他们试图建立原型并找出最佳的整体布局。第二个工具叫做Xpedition Package Designer,它的目的是让你惊喜!-设计包装的人。

PCB当然是整个交易的一部分,但已经有一个Xpedition PCB与此相关。这三个域的相互作用如下图所示。

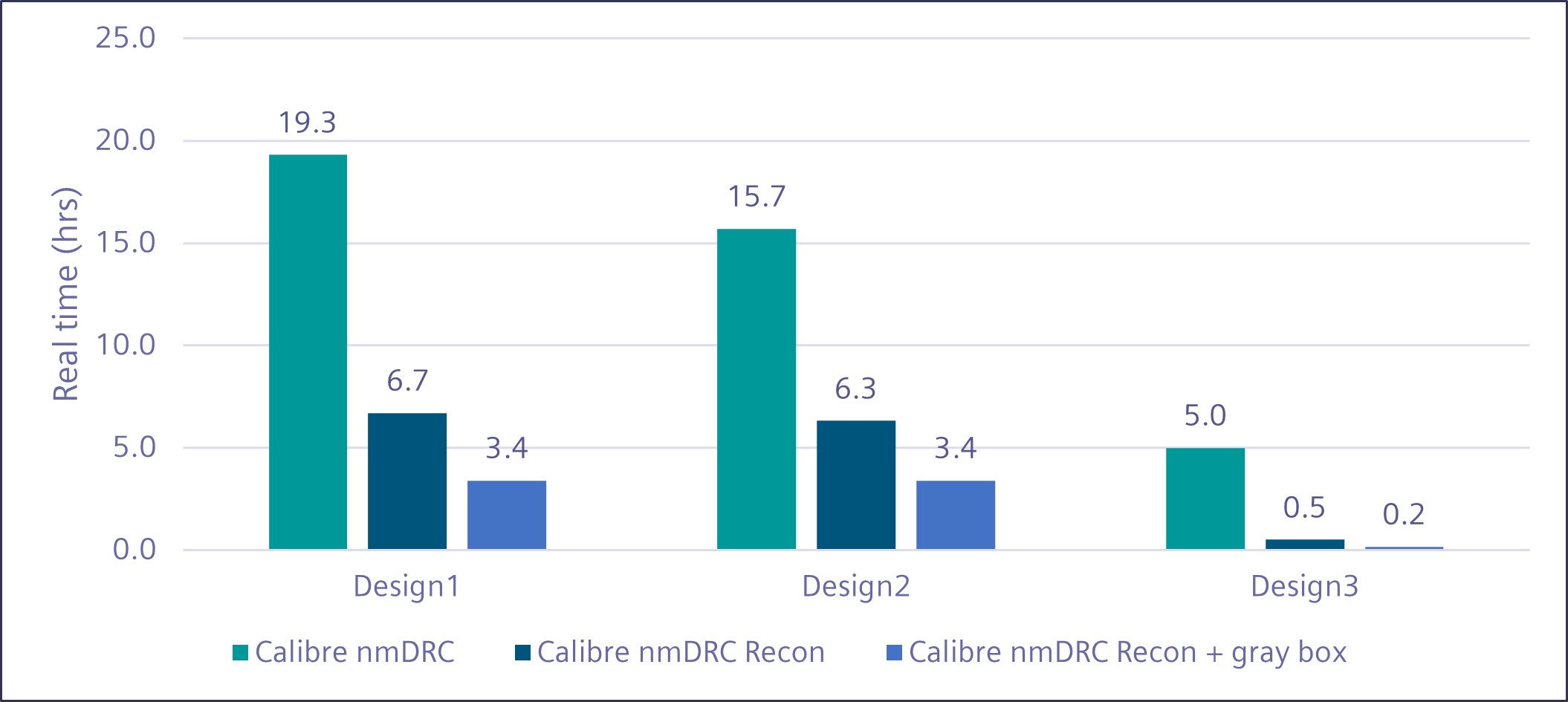

设计规则检查(DRC)有两种不同的实现方式。据Mentor公司介绍,HyperLynx DRC可以快速解决85%的问题。签字时,这个交给Calibre。在这个低级别上,所有内容都是Calibre需要的格式,因此不需要Calibre的新版本。

Xpedition和Calibre之间的一个区别是,Xpedition可以在Windows或Linux上运行;Calibre只能在Linux上运行。Mentor通过实例化一个用于托管Calibre的Linux虚拟机,在Windows系统上解决了这个问题。这一切都是不透明的;你真的不需要担心那个细节。

验证所涉及的不仅仅是过去足够的打开和卖空测试。如今,还有其他事情需要检查,比如确保金属密度的平衡,以防止晶圆翘曲。是啊,谁知道呢。

来自Cadence和Mentor的这两个工具似乎有不同的关注点。如果我将注意力集中在每个焦点所体现的基本验证方面,Cadence是关于整体集成模块上下文中的模拟电气验证;Mentor是关于布局和drc的,特别是关于硅衬底。也就是说,它们都能够与相应的工具一起处理整个流程。

无论哪种情况,筒仓的墙壁都在坍塌。每个领域仍然需要不同的技能,但现在他们需要合作,以在合理的时间内获得他们想要的结果。

更多信息:

你怎么看待Cadence和Mentor将骰子集成到高级包中的工具?