正如我所注意到的,成为我的一大好处——除了超级帅、潮流引领者和时尚领袖之外——就是我可以和各种有趣的公司和个人谈论他们超酷的技术。

我脑海中浮现出两个相关的例子:在SiMa.ai他们的目标是创建一个机器学习(ML)片上系统(SoC)MLSoC这可以在嵌入式边缘提供毫不费力的机器学习,而在Arteris IP它的使命是提供最先进的技术半导体IP而且IP部署技术.

让我们从司马氏说起。ai成立于2018年,就在我写下这些话的时候,才短短四年。司马的人。ai表示,现有的ML解决方案并不是专门为嵌入边缘而设计的,而是针对它进行了适应,在概念上类似于将方钉插入圆孔。他们建立司马时的目标。ai的目标是通过提供“世界上第一个以软件为中心的、专门构建的MLSoC平台,具有按钮性能,可以轻松地进行ML部署和在嵌入式边缘扩展,以便您可以更快地将产品推向市场”来简化将ML添加到产品中的过程(暂停,深呼吸)。

简而言之,他们想要设计一个MLSoC,它可以运行任何计算机视觉应用程序、任何网络、任何模型、任何框架、任何传感器和任何分辨率。更具体地说,他们希望为用户提供解决任何计算机视觉应用挑战的能力,在每秒每瓦帧数方面比任何竞争产品至少高出10倍,同时在几分钟内提供全面的按钮体验。那么,他们的表现如何?

最近,我和Srivi Dhruvanarayan聊天,他是SiMa.ai的硬件工程副总裁。正如Srivi所说,这意味着与mlsoc的硬件方面有关的任何事情——从架构到逻辑设计到逻辑验证到物理设计到物理验证,再到提出——都是他的责任。

在许多ML应用程序中,大多数繁重的工作是由主机处理器执行的,只有以ML为中心的算法部分被卸载到ML加速器。相比之下,MLSoC的关键区别之一是它是一个完整的系统,在一个设备中结合了主机处理器和ML加速器功能。另一个关键的区别是它们在非常低的功率下完成所有这些工作。

带有深度神经网络(DNN)加速器的嵌入式视觉处理器(EVP),以及……一大堆其他IP块。

MLSoC高级框图(来源:SiMa.ai)

在16nm技术节点上创建的整个MLSoC由数十亿个晶体管组成。这一切的“秘密武器”是MLA,它能提供每秒50万亿次运算(TOPS),而消耗的功率只有区区5瓦。

上面所示的简单框图只反映了主要的IP块。它还设法使事情看起来漂亮和干净——“简单的柠檬挤压”,因为它是。真正的诀窍是将所有这些IP块连接在一起,如果你做得不对,最终会让你有一个“压力抑郁的柠檬味”的日子。

当涉及到在SoC内连接IP块时,有三种主要方法。第一种是使用简单的总线,下图中标记为“总线”的线路包括多根导线,用于传输任何地址、数据和控制信号。

基于总线的SoC互连(架构来源:Max Maxfield)

这种基于总线的技术是我们在20世纪90年代使用的方法。它仍然适用于只有一个(或很少)启动器IP块的简单设计,其中所有的启动器和目标IP块都支持相同的接口(即,以相同频率运行的相同总线宽度)。

基于总线的互连开始失去动力,因为设计开始变得越来越复杂,有多个启动器和许多目标。大约在2000年代采用的主要解决方案之一是使用基于交叉开关的互连架构。

基于交叉开关的SoC互连架构(来源:Max Maxfield)

和前面一样,每一行表示多个信号。交叉开关提供了显著的优势,包括任何发起者都可以与任何目标通信,并且多个事务可以同时“运行”(如果多个事务同时到达,交换机有缓冲事务的能力,并确定它们的相对优先级)。

不幸的是,就像他们的基于总线的祖先一样,交叉开关架构只能做这么多,而且它们不能充分服务于今天的高端SoC设计,这些设计具有杂乱的启动器和成群的目标。在某些阶段,有如此多的启动器和目标,将它们连接在一起会导致互连消耗超过其公平份额的硅,再加上路由拥塞,会让你流泪(只是要清楚,这些不会是高兴的眼泪)。

这些问题只会因为不同的IP块而加剧,这些IP块总是来自不同的第三方供应商,可能支持不同的接口(宽度、频率、协议)。在20世纪90年代,一个SoC可能只包含几个IP块,整个设备可能只包含2万到5万个逻辑门和寄存器。相比之下,当今的高端soc可以包含数百个IP块,每个IP块可能包含数十万(有时是数百万)逻辑门和寄存器。

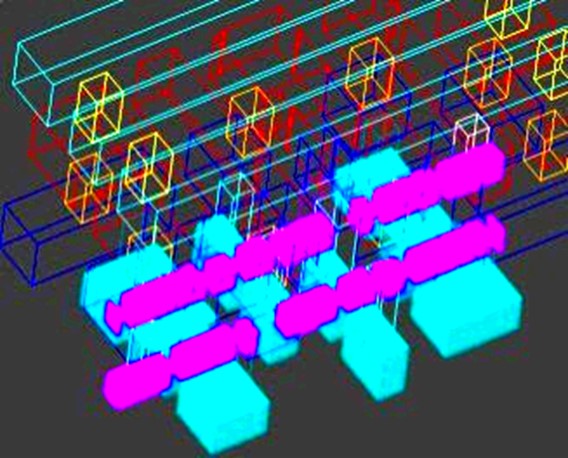

所有这些都将我们引向目前最先进的SoC互连,以片上网络(NoC)的形式(在对话中,“NoC”与“时钟”押韵)。每个IP块通过“套接字”与NoC连接,该套接字处理诸如宽度转换、协议转换、命令转换和时钟域交叉(不同的IP可以在不同的频率上运行)等事情。

简单的片上网络(NoC)互连架构

(来源:Max Maxfield)

启动器和目标之间的事务以“包”的形式发送,每个包包含一个头部(指定目的地地址)和一个主体(包含请求类型、数据、指令等)。多个数据包可以同时“在飞行中”,而且——同样地——如果多个数据包同时到达,交换机可以确定它们的相对优先级并缓冲低优先级的数据包。

通常情况下,如果你大声说话,大声打手势,这听起来很容易,但开发自己的NoC不是一件简单的任务。Srivi告诉我,他在之前的公司参与了一个NoC的开发,这需要六到七个人花近两年的时间来构建、设计和验证这个NoC。

在硅镁层。在ai上,Srivi希望他的团队专注于MLA的设计和MLSoC的实现。因此,他开始四处寻找强大、灵活、健壮的NoC IP,以使团队能够通过许多不同的接口无缝连接来自许多不同来源的IP块。没过多久,斯里维就被介绍给了FlexNoC互连IP从Arteris。

作为一个简单的经验法则,无论设计中的IP块是否采用AMBA AXI3, AXI4, AHB, APB, OCP, PIF或专有协议的混合,Arteris FlexNoC IP减少了近一半的导线数量(与次优互联策略相比),导致更少的门和更紧凑的芯片布局(这可能解释了为什么目前超过70%的汽车SoC设计使用Arteris系统IP)。

FlexNoC的优点之一是,它允许SoC开发人员通过快速、轻松地评估不同的NoC实现来探索解决方案空间(例如,一个大型NoC vs.多个小型NoC)。FlexNoC还配备了一个方便的性能分析功能,可以帮助开发人员确定他们的各种“管道”和“高速公路”是否足够大、足够快,以实现他们的性能目标。

俗话说:“布丁好不好,尝一尝才知道。”好吧,据我所知,一个充满FlexNoC的比喻布丁确实是一种美味的款待。正如Srivi所说,“我们公司成立于2018年,我们在短短三年多的时间里设计了可以说是地球上最复杂的soc之一,我们在2022年2月制作完成,并在2022年5月收到了第一块硅,这一切都要感谢我们出色的合作伙伴,如Arm、Synopsys和Arteris。在零bug的情况下,我们继续朝着第一次成功的方向前进,直接投入生产。就在收到第一块硅片的六周后,我们就在客户的实验室里运行他们的端到端应用程序管道,并以我们承诺的10倍优势让他们大吃一惊。”

完全披露:我不打算很快自己开发一个数十亿晶体管的SoC。然而,如果我是,NoC将成为我设计的关键元素,我认为可以相当肯定地说,这个NoC将使用Arteris的FlexNoC Interconnect IP实现。你说呢?您目前是否参与设计soc ?如果是这样,你们将如何应对自己的芯片互连挑战?