在过去的几年里,3D技术已经被广泛应用。我们可以忽略3D电视热潮,它就像一个转瞬即逝的化身。但这两种IC表现是3D晶体管(即finfet)和3D封装集成-堆叠芯片。

后者是一种超越摩尔技术,允许多个芯片,每个芯片都建立在最适合它的进程上,能够利用大量现成的骰子,如内存,而不是从头开始设计。

但是如果你想要像电路一样垂直伸缩呢?也就是说,那些货架上没有的东西都需要相同的流程?你要么在单个芯片上横向构建它们,要么构建多个芯片并堆叠它们。

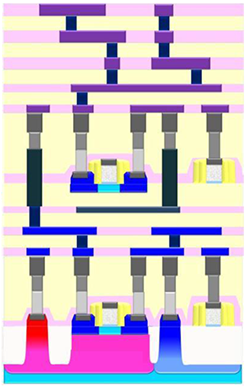

Leti正在研究另一种选择:单片3D集成。这相当于建造一个标准芯片,然后在上面生长一层新的硅(或其他东西),然后建造更多的电路。在概念上听起来很简单,但想象起来比实现起来容易。他们在最近的Semicon West聚会上展示了自己的地位。

图片由Leti提供

这些想法中最大的问题就是热量。对于底层,你制造晶体管,植入掺杂剂,然后用热量“激活”它们,让它们移动到它们应该在的地方。在那之后,你希望他们呆在那里。如果你一直开着火,它们就会不停地移动,所以一旦它们凝固了,你就不想再加热了。

显然,人们还担心在额外的热量下接触水杨酸盐的稳定性。

额外的热量从何而来?

当你制造下一层晶体管时,你需要给它们涂上涂料并再次激活。如果你的底部晶体管已经在你想要的地方了,额外的激活会把它们搞砸。你试着不激活底部的那些,希望第二次激活能让它们保持一致吗?

这不是莱蒂采取的方法。他们正在试验“crème brulee”技术:使用肉鸡进行第二层激活。也就是说,热量来自顶部,这样在足够短的时间内,只有顶层被激活,热量不会扩散到下面,破坏下面的晶体管。

与现有流程的兼容性是另一个需要考虑的问题。你必须能够连接上晶体管和下晶体管,而理论上,目前还没有这样的互连。他们没有定义新的互连,而是利用该部件的本地互连(LI)。

最后,一个大问题是:如何构建和排列晶体管和CMOS对,以及其他像NEMS器件这样可能想要在同一芯片上运行的元素?他们有三种不同的构型。

第一个是“CMOS over CMOS”。换句话说,在同一层(顶部和底部)上构建N和P种类型。他们列出了FinFET优于FinFET, Trigate/纳米线优于Trigate/纳米线(所有SOI),或FDSOI优于FDSOI。但他们也有一张图显示了FDSOI晶体管在FinFET上。他们的指控是,两层14纳米技术提供了一层10纳米技术的缩放。

第二种选择是通过在不同的层上设置N和P类型的晶体管来优化晶体管。因此,尽管第一种选择的CMOS对是横向构建的,但在第二种选择中,它们是垂直构建的。这使得他们可以在两层上使用不同的材料。他们已经尝试过用锗(Ge)代替P而不是硅来代替N。他们还利用了不同的晶体取向,用硅[110]代替P,用硅[100]代替N。下一步,他们将尝试用InGaAs代替N / Ge来代替P。

第三个选择涉及到在CMOS上集成NEMS。我们看了他们的M&NEMS项目去年(这项工作仍在继续)。

他们已经做了一些FPGA的工作,看看他们能得到什么样的改进。他们使用了两层堆叠的FDSOI层和两层钨锂。它们将面积提高了55%(这并不奇怪),但也将性能提高了23%,功率提高了12%。赢赢赢。显然是在处理当地事务。

我们会在看到新的结果时进行更新。