如果你想减少系统的功耗,你不能等到你的设计减少了盖茨。是的,你可以做一些事情来帮忙的,但最终的胜利之前,在建筑或RTL的水平。

但是你怎么知道这一点目前的设计将画多少钱?特别是,动态电流?过去的方法使用平均活动速率或一些这样的一般数量给squint-your-eye近似,但很难得到正确的数量,很难使它正确mode-by-mode和事情。

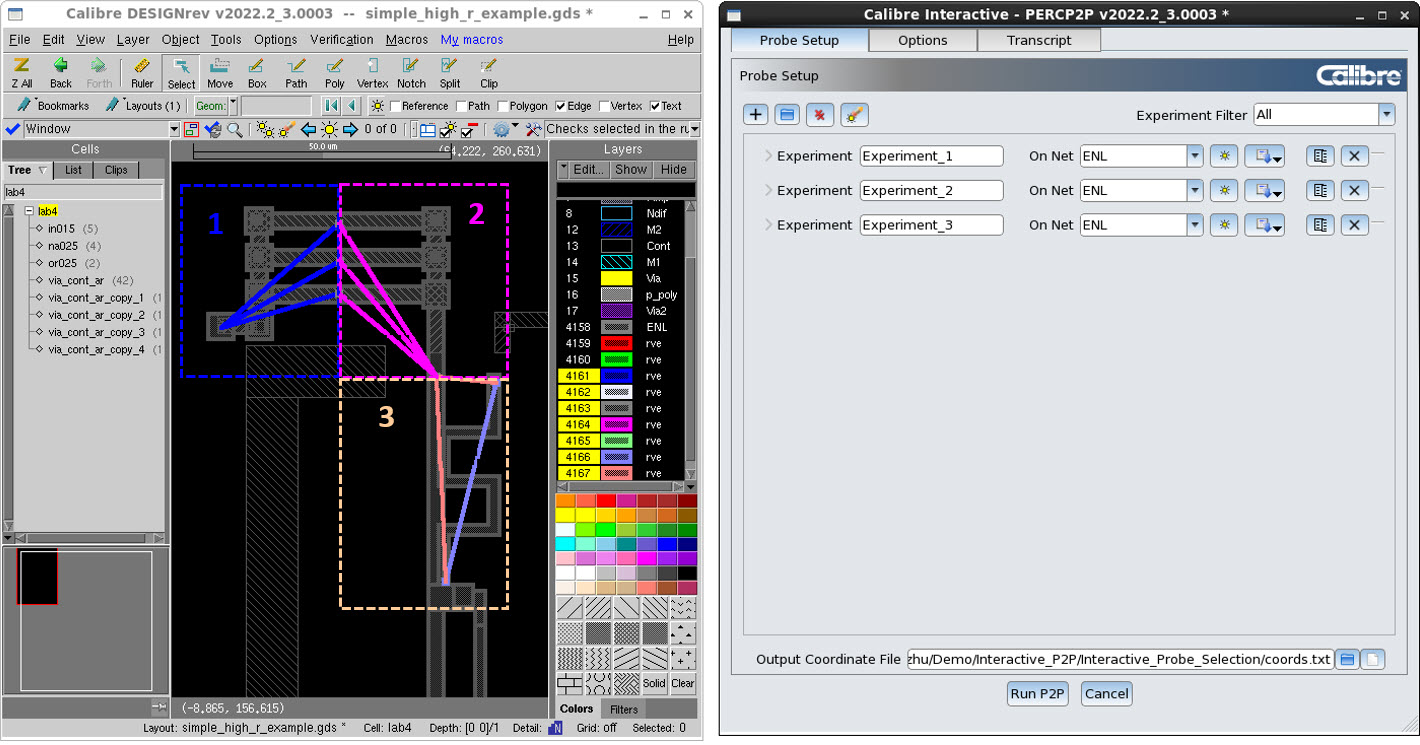

什么是好是实际的活动数据。这意味着访问每个节点的设计,包括所有节点可以有他们的力量贡献。FPGA原型是行不通的,因为所有的节点不是外部可见。导师指出,即使fpga仿真器,像Synopsys对此的瘤牛系统,不会因为他们的全面了解工作方法依赖于JTAG流内部,这将是非常缓慢的做每个节点在每个周期。(需要注意的是,导师和Synopsys对此有一个不一致的历史模拟专利声称…)

导师说,他们快速的仿真器可以运行一套测试速度,但仍然有一个问题:捕获结果分析工具中使用的权力。传统方法这将捕获一个FSDB(快速信号数据库)文件,然后使用该文件作为输入功率分析。但这将是一个极大的文件,写作和阅读会成为病原反应步骤(部分原因是数据是由信号但阅读时间)写的。

替代使用VCD(仍然太慢)或赛义夫(切换活动交换格式)。赛义夫只给出平均活动信息。更详细的可以通过提供更多的结构信息提前通过“赛义夫”文件,但导师说,建立这个文件需要整个设计的详细知识,可以耗费时间。所以这些传统方法往往仅用于模拟有限的数以1000年的周期。

导师的快速的活动图有助于减少数据快速显示所需的活动范围是最大的(没有深刻的细节)。然后您可以隔离这些地区和快速地重新运行这些关键时期详细,这样可以确定。但这仍然是一个多FSDB或VCD方法可以处理优雅。

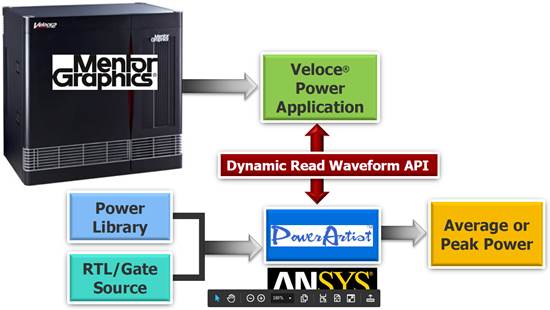

所以导师做了一些非比寻常:他们与敌人称兄道弟。谨慎。一般来说,他们与Ansys竞争,但他们不与Ansys的PowerArtist实力竞争分析工具。他们希望能够传送数据,工具没有泄露的内部数据和结构化存储。所以他们掩盖所有的细节通过提供一个API, PowerArtist可以使用它来捕获数据。

换句话说,没有更多的保存一个文件作为中间步骤:模拟器上的电路活动是观察并通过实时PowerArtist,电力计算结果。

(图片由导师图形)

导师调用这个工具快速的电力应用程序。这不仅仅是一个导师实用程序覆盖现有PowerArtist安装(单独出售);这是一个完全整合。所以当你得到导师的工具,你也得到PowerArtist工具埋在里面。

你可以得到更多的信息在他们的公告。