很少有半导体电路像SRAM电池一样稳定。直到现在。

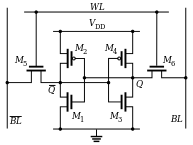

SRAM很重要,因为它是我们性能最快的内存层——它可以占用你SoC的很大一部分空间。但这是一种昂贵的野兽(否则我们会使用更多)。只要我能回忆起,SRAM位的基本参考电路一直保持不变。它需要6个晶体管,排列成一对背靠背的逆变器,带有交叉耦合反馈来保持状态。

(图片来源:维基百科)

在这个单元上进行了许多调整和优化,但多年来一直保持着顽强的一致性。然而,现在,我第一次看到,一项提议摆在桌面上,宣布一家名为Zeno的初创公司在IEDM推出了一种新的SRAM单元。一个与我们所了解和喜爱的完全不同的人。而且它只需要一个(或两个)晶体管。

认真对待。我们先不考虑5个或3个晶体管的中间点;不,让我们从6跳到1吧。

而且,如果你想知道,这不是一个伪装的DRAM;它是真正的静态,具有非破坏性的读取和无刷新要求。

是的,我看到你眯起眼睛怀疑。如果一个晶体管就能做到,为什么我们现在才发现呢?硅的奇异生产技巧和超材料在这里发挥了什么作用?

嗯,听芝诺说,他们的新牢房里可没有这样的东西;这与现有的CMOS产品完全兼容。它需要一个额外的非关键的蚀刻步骤和一个额外的植入。CMOS的兼容性是通过建立在梭式晶圆上的原型芯片和其他CMOS电路来证明的。

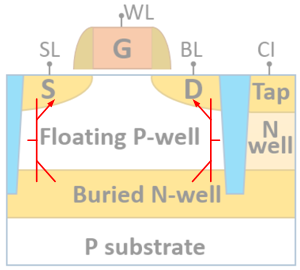

这到底是怎么回事?他们之所以调用Bi-SRAM,是因为他们构建的结构中有一个固有的双稳态双极晶体管。他们取一个基本的MOSFET,然后在下面植入一个n孔。埋置的n阱、p阱和源/漏区组成了NPN双极晶体管。

(图像组件由IEDM提供)

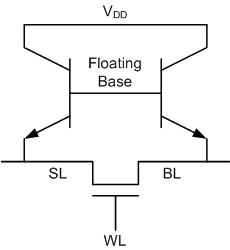

简单地说,我喜欢这样画。(这与他们展示的方式相反,但对我来说,更容易想象双极晶体管集电极的一面朝上。)

说到底,这个想法很简单,它取决于那个浮动的基座。你可以把它想象成承运人的一个正常封闭的集装箱。在一个州,基地里装满了航母。这将打开双极晶体管,打开一个电流路径通过埋层(连接到VDD或者叫它VCC?)在另一种状态下,浮动基耗尽载波,关闭双极器件。你通过MOSFET读取状态。如果有很多电流,那么其中一些电流会通过集电极。

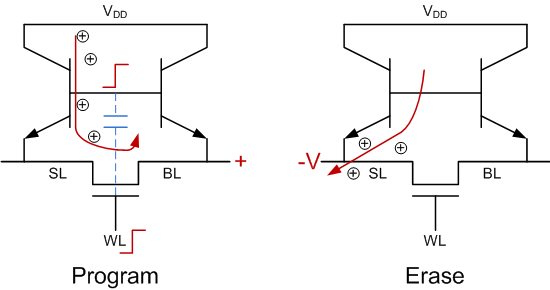

这是底层的状态机制,但您还需要能够编写这种状态——也就是说,要么用载流子填充浮动基区域,要么耗尽载流子。他们通过利用FET门和浮动p阱之间的电容来做到这一点。

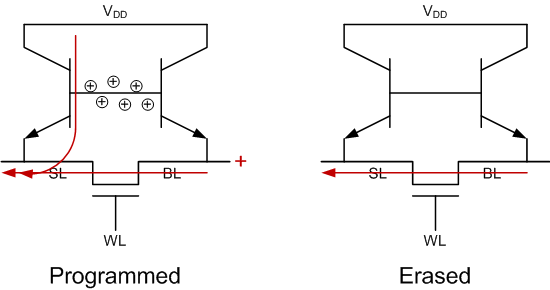

他们没有详细介绍算法,所以这是我对他们高级描述理解的超级简化总结。他们编程一种状态,通过提高单词线和上升-呃-提高一个仔细控制的上升时间-单词线。这与浮动底座耦合,打孔底座并打开双极晶体管。这变成了一种自我维持的状态,基于从收集器流入的载波,现在锁定在浮动基座上。

为了写出相反的状态,你将源线拉到负电压,将载波从基极中抽离,断开双极晶体管。是的,你发现了,是吗…这确实需要一个负电压泵。大约有6-8%的细胞支持电路,所以你不会得到一个完整的5/6大小缩小净净。只有4/5。希望你能接受。

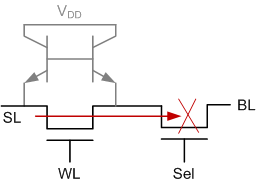

所示细胞的性能与正常的6T细胞大致相当;可能有点慢。对于高性能应用,他们有一个更高速度的版本,增加了一个额外的选择晶体管。1T版本显示漏电流通过通道上的未选择的细胞,这使得一个较慢的读取。选择晶体管切断泄漏,增加电流的动态范围,这使得它更容易-更快-读取。

虽然这样晶体管的数量增加了一倍,但他们可以通过一些巧妙的布局来缓解这种影响;他们称之为1.7 t细胞,因为它只有基本1T细胞的1.7倍大。但是,作为奖励,它比6T细胞快40%。

所以,取决于你选择的设备,它总是小于6T(除以5或2.5),但可能会稍慢或快40%。在一个28纳米节点中实现,1T细胞的面积为0.025µm2;速度较快的电池为0.044微米2。

与此同时,静电功率下降了五分之一(对每个电池来说)。动态功率大致与6T相同;也许再低一点。对于一个消耗电池的物联网边缘节点来说,大部分时间都是坐在那里打瞌睡——嗯——静止不动,所以在一个大(虽然现在小了)硅块上节省五分之一的功率可能是令人兴奋的。

现在,我知道你在想什么:也许这适用于28nm节点。但是未来的节点呢?这其中是否有可能破坏一两个节点?那么FinFET呢?他们说,他们的方法可以扩展到新的节点,并且他们可以为finfet创建类似的双稳态机制。他们没有看到明显的日落条款。

最后一个我天真地问的问题是:这只适用于嵌入式应用程序,还是也适用于独立的sram ?

答案是,“谁还在使用独立的SRAM?”好吧,对一些玩家来说,这仍然是一个很好的业务,这项技术可以在那里使用。但这并不是嵌入式SRAM市场的增长领域。因此,他们的重点仍将放在嵌入式方面。

你可以想象,这是一个授权游戏,所以,在揭开面纱之后,这些人现在正忙着与潜在的被许可方谈判。这可能会吸引一些人的注意,这可能不足为奇。如果一切都如承诺的那样,这可能是作用于市场的罕见的冲动函数之一。有一天,你可能会告诉你的孙子,当sram从六个晶体管变成一个晶体管的时候,你就在那里……非常戏剧性的事情。

更多信息:

你觉得芝诺的1T SRAM电池怎么样?

真正大量使用静态ram的不是处理器的分页表和缓存吗?也许是FPGA的控制存储器?

很好奇在6T设计上SEU是否有什么好处。

如果本质是基区的电荷,那么为什么这个电池比动态RAM电池更好呢?

或者为什么需要2个npn晶体管,而不是一个?

在我看来,门端负电压迫使一些准电流源,它馈电晶体管的基极。正栅极电压使两个晶体管网络处于某种稳定状态,其中一个晶体管的基极电流最小。

谢谢你的评论。

关于SEU,目前我们还没有进行SEU测试。然而,由于SEU的横截面面积更小,我们预计SEU比6T-SRAM更有优势。

对于DRAM比较,单元是静态的,因此不需要刷新操作。读取操作也是非破坏性的。

静态行为由埋在地下的n阱、p阱和源/漏区形成的npn双极控制。由于MOS有源极和漏极,所以有2个双极,但1个足以实现双稳定。

我们将更新我们的网站(www.zenosemi.com),提供更多关于双稳定机制的细节。请稍后再来查看。

-Yuniarto

从原理图和占地面积两方面来看,与传统的6T SRAM单元相比,3T不是更好吗?

就功能而言,你是正确的,它可以被认为是3T。但占地面积为1T (28 nm时电池尺寸为0.025um2, 6T时电池尺寸为0.127um2)。本文中的单元图包括一个在许多存储单元中共享的井孔接头。

你要依靠漂浮的微粒来储存电荷。根据存储的电荷量,它仍然可能通过栅极以及SD和埋层结泄漏出来。如果被埋的层被供电到VDD,它可能会泄漏电荷到浮动的pwell中,将一个未编程的单元转换为程序单元。我们在部分耗尽的Soi晶体管中看到了这种现象。从本质上讲,这是一个动态RAM等效,但可能占用4f2的空间,而不是大多数dram的6f2。

历史上,深NWELL有更多的管道(由于注入能量较高而产生缺陷),这将加剧泄漏到浮井的路径。它将非常依赖于退火工艺,而常规cmos对埋层缺陷的敏感性要低得多。