我很高兴(尽管有些困惑)告诉你,在验证FPGA、ASIC和片上系统(SoC)设计方面,情况似乎越来越好。我之所以这么说,是因为上次我把注意力转向这个领域时,人们说一个复杂设备的设计和验证阶段分别消耗了总开发时间的30%和70%。相比之下,最近有人告诉我,这些数字现在更接近50%和50%,这意味着我们要么在验证方面做得更好,要么在设计方面做得更差。

您可能还记得,大约六周前,当我写下这些文字时,我在挪威的FPGA论坛上做了主题演讲(参见没发生什么,还是真的发生了?和所有的改变!和当超级计算机遇到啤酒Pong).当我在那里的时候,我参加了各种各样的演讲,其中一个是我的老朋友做的埃斯Tallaksen他是微软公司FPGA和空间技术的首席执行官、联合创始人兼总监EmLogic(如果你想知道,它代表的是“嵌入式逻辑”)

EmLogic是一个独立的嵌入式系统设计中心,特别是fpga。虽然EmLogic是一个相对较新的公司,于2021年1月1日成立,但它已经成为挪威和斯堪的纳维亚地区领先的FPGA设计中心。EmLogic还在FPGA设计和验证方面成为领先的培训提供商,在全球各地的公共教室、现场或在线开设课程。

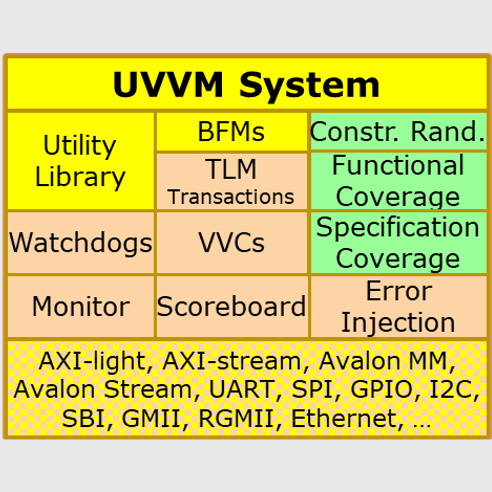

除了设计咨询和服务,EmLogic还是一个验证IP和方法的提供商UVVM(通用VHDL验证方法),这是一个用于验证fpga和asic / soc的开源库和方法GitHub.此外,除了是FPGA论坛的发起人和主席,Espen也是UVVM的最初作者和架构师。

当Espen开始他的演讲时,他用一张包含了一些引用的幻灯片开场,包括“软件设计师用恐怖的眼光看待其他代码”和“RTL设定了糟糕的新标准”以及“大多数设计对另一个设计师来说几乎是无法理解的”。我必须承认,我同意所有这些引用,这是偶然的,因为原来Espen引用了我的书fpga设计战士指南.

Espen说,很明显,我们必须进行大量的验证,但当涉及到创建验证套件、定义测试工作台和调试设计时,我们可以更加高效。

说句题外话,当我在2012年参加的第一届FPGA论坛上第一次见到Espen时,有一件事让我感到困惑,那就是他有苏格兰口音。我在最近的一次访问中想起了这一点。起初,我以为这可能是挪威人说英语时的发音方式。然而,事实证明Espen在格拉斯哥大学学习,所以这是一件让我担心的事情,但我们离题了……

当涉及到验证FPGA或ASIC/SoC设计时,您将围绕被测设计(DUT)拥有某种验证基础设施——将数据写入DUT的东西,从DUT读取响应的东西,以及控制不同测试和报告任何结果的东西。您希望从验证环境和解决方案中获得的关键方面是可读性、可理解性、可修改性、可维护性、可扩展性、可调试性和可重用性。

UVVM提高了质量和效率(来源:EmLogic)

我必须承认,当今超级复杂的FPGA和ASIC/SoC设计的验证不是我的专业领域,但我会试图传达一点关于这一切的暗示。我们将以Utility Library的形式从基础/入口级开始。

假设设计包括一个简单的中断控制器(IRQC)模块,如下所示。让我们假设这个控制器有一个时钟输入,一个异步复位,一个简单的总线接口(SBI)用于外部CPU到达它的内部寄存器,n个不同的中断源,结果中断到CPU。

测试排序器代码和记录日志的示例(来源:EmLogic)

UVVM实用程序库包含一堆函数和过程,可以用来构建一个测试平台来练习这个IRQC模块。我们从一个时钟生成器开始,它可以通过从Utility Library(灰色框中的语句)调用一个过程来实例化。接下来,我们创建测试排序器,它由一组过程调用(橙色框中的语句)组成。当测试序列运行时,结果显示在记录日志中(蓝色方框)。(请注意,这是一个简化的转录-还可以设置/显示前缀、消息id和范围。)

能够使用这些预定义的函数和过程构建测试平台,极大地简化了设计IRQC模块的人员的工作,并允许他们比必须自己创建测试函数和过程更快地验证模块。

请记住,这只是UVVM入口级的一个示例。接下来,我们有一个丰富的总线功能模型(BFMs),伴随着大量支持的接口(axis -light, axis - Stream, Avalon MM, Avalon Stream, UART, SPI, GPIO, I2C, SBI, GMII, RGMII,以太网……)这些软件也是开源的,免费的。

除了评估功能覆盖和规范覆盖之外,UVVM还拥有复杂的约束随机功能,包括向随机值添加权重的能力。

我担心我们只是触及了这个话题的表面,但我们已经达到了我可以有知识地谈论的边界。只需说明,您还可以设置检查DUT的同时活动,这意味着系统可以同时在多个接口上启动事务(或根据需要倾斜它们),以根除任何有问题的角落情况。

Espen大约在15或16年前开始研究UVVM。它在2015年首次以开源的形式发布,从那时起,它的使用就突飞猛进。

Mentor Graphics(现在的西门子EDA)使用了一家名为威尔逊研究每两年对ASIC/SoC和FPGA的发展进行一次调查。威尔逊研究公司的人会考虑很多不同的方面,比如有多少人在使用不同的语言,以及他们发现的错误类别。他们关注的一件事是有多少人在使用各种验证系统。在2020年的调查中,UVVM在VHDL验证方法中名列前茅。

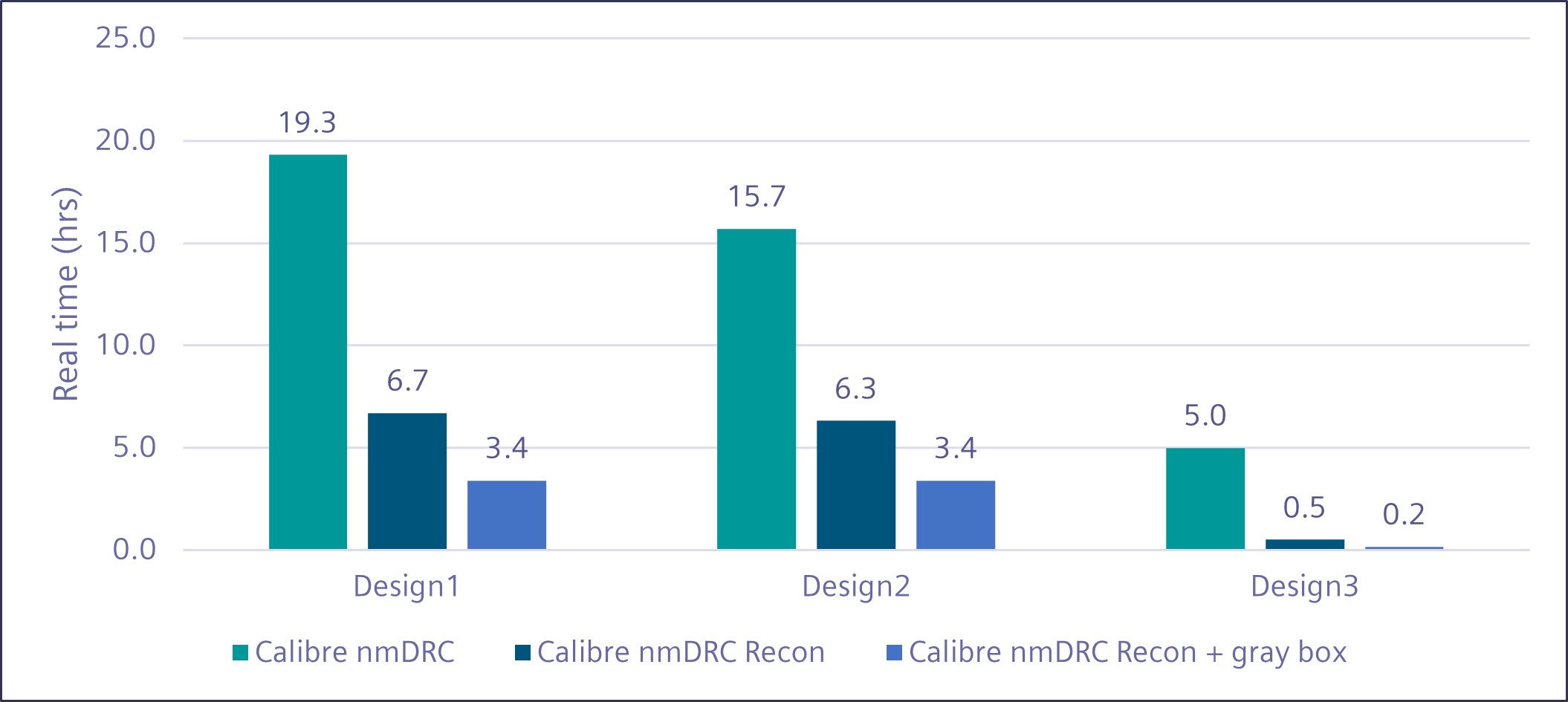

FPGA验证方法,全世界,所有语言(来源:EmLogic)

2020年的调查结果显示,UVVM是全球VHDL验证的#1。Espen开玩笑说,大约20年前,有人告诉他VHDL正在消亡,他应该开始使用SystemC。如今,根据威尔逊研究公司(Wilson Research)的数据,全球超过50%的设计师使用VHDL。Espen说,在欧洲,这一数字在80%到90%之间。即使在Verilog和SystemVerilog的堡垒美国,VHDL也通常用于军事和航天项目。此外,UVVM是独立于语言的增长最快的验证方法,在2018年至2020年调查之间的两年里,其使用量激增了100%。

我在验证空间(没有人能听到你的尖叫)的英雄之一是布莱恩•贝利.我不认为说布莱恩是世界上最重要的核查权威之一是夸张的。事实上,我参加了一个关于SCAN设计的培训课程,这是Brian在大约40年前提出的(在那里做时间流逝了吗?)我还没有机会和Brian谈论UVVM(我相信他知道这一切),但我会在最早的机会这样做。与此同时,我很想听听你对这一切的看法。