亮点:

Cadence 3D-IC解决方案以Integrity 3D-IC平台为中心,提供集成规划、实施和系统分析,以优化多芯片系统的PPA

●Tempus定时终止解决方案,具有模具间分析和STA技术,可缩短带出时间

Voltus IC电源完整性解决方案,与摄氏度热求解器紧密结合,促进多模红外下降和热分析的设计鲁棒性

●客户可以放心采用Cadence 3D-IC解决方案和TSMC 3DFabric技术,创建下一代超大规模计算、移动和汽车应用

加利福尼亚州圣何塞10月27日消息——cadence Design Systems, Inc.(纳斯达克代码:CDNS)今天宣布与TSMC合作,加速3D-IC多芯片设计创新。作为合作的一部分,Cadence®Integrity 3D- ic平台是业界首个用于3D- ic规划、实施和系统分析的统一平台,可用于台积电3DFabric技术、台积电全面的3D硅堆叠系列和先进的封装技术。此外,Cadence Tempus计时签收解决方案已得到增强,以支持新的堆叠静态计时分析(STA)签收方法,缩短设计周转时间。通过这些最新的里程碑,客户可以放心地采用Cadence 3D-IC解决方案和台积电的3DFabric技术,创建具有竞争力的超大规模计算、移动和汽车应用程序。

Cadence 3D- ic解决方案支持台积电的全套3D硅堆叠和先进的封装技术,包括集成扇出(InFO)、晶圆上基板(CoWoS®)和系统上集成芯片(TSMC- soic™)。3D-IC解决方案也符合Cadence智能系统设计策略,推动芯片上系统(SoC)设计的卓越性。

Cadence Integrity 3D- ic平台在单一统一的座舱中提供3D芯片和封装规划、实现和系统分析。这使得客户可以简化3D硅堆叠的多芯片设计规划、实现和分析,同时优化工程生产率、功率、性能和面积(PPA)。此外,该平台还具有与Cadence Allegro®包装技术和Cadence Virtuoso®平台集成的协同设计功能,可实现完整的3D集成和包装支持。有关Integrity 3D-IC平台的更多信息,请访问www.cadence.com/go/Integrity3DICpr。

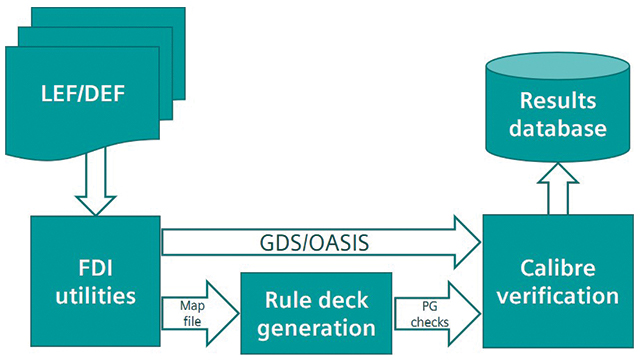

为了进一步造福客户,Cadence分析工具与Integrity 3D-IC平台紧密集成,并与TSMC 3DFabric技术无缝协作,实现系统驱动的PPA。例如,Tempus Timing sigignoff解决方案集成了快速自动模间(RAID)分析,这是Cadence 3D STA技术的一部分,可以帮助客户创建具有精确定时终止的多层设计。Cadence Celsius™热求解器能够支持多芯片堆叠、soc和复杂3d - ic的分层热分析。在层次分析中,热点用更细的网格建模,这使客户能够实现运行时和精度目标。Cadence Voltus的IC电源完整性解决方案为客户提供热,IR下降和跨模电阻分析,以实现设计的鲁棒性。有关Cadence 3D-IC解决方案的更多信息,请访问www.cadence.com/go/3DICsolpr。

台积电设计基础设施管理部门副总裁Suk Lee表示:“台积电和Cadence的这次合作证实了Integrity 3D-IC平台、签到和系统分析工具支持台积电先进的3DFabric芯片集成解决方案,为我们的共同客户提供灵活性和易用性。”“我们与Cadence长期合作的结果使设计师能够充分利用台积电先进工艺和3DFabric技术在功率、性能和面积方面的显著改进,同时加速创新他们的差异化产品。”

Cadence高级副总裁兼数字与签名集团总经理Chin-Chi Teng博士表示:“通过努力确保我们的Integrity 3D-IC平台支持台积电3DFabric技术,我们正在推进与台积电的长期合作,并促进几个新兴领域的设计创新,包括5G、AI和物联网。”台积电的3DFabric产品与Cadence的集成高容量Integrity 3D-IC平台Tempus搭配使用

Timing Signoff解决方案,Allegro封装技术和3D分析工具为我们的共同客户提供了一个有效的解决方案,可以部署3D设计和分析流程,以创建健壮的硅堆叠设计。”

关于节奏

Cadence是电子设计领域的关键领导者,拥有30多年的计算软件专业知识。该公司应用其底层智能系统设计策略,提供软件、硬件和IP,将设计概念变为现实。Cadence的客户是世界上最具创新精神的公司,为最具活力的市场应用提供从芯片到电路板到系统的卓越电子产品,包括消费、超大规模计算、5G通信、汽车、移动、航空航天、工业和医疗保健。《财富》杂志连续七年将Cadence评为最适合工作的100家公司之一。更多信息请访问cadence.com。