亮点:

与上一代Palladium Z1和Protium X1系统相比,新的动态双机提供了2倍的容量和1.5倍的性能提升

基于新的自定义仿真处理器的Palladium Z2仿真提供了最快、最可预测的编译和最全面的硅前硬件调试功能

Protium X2原型基于最新的Xilinx UltraScale+ VU19P fpga,为数十亿门设计的预硅软件验证提供了最高的性能和最快的启动时间

Cadence为IP和SoC验证、硬件和软件回归以及早期软件开发提供了最全面的解决方案

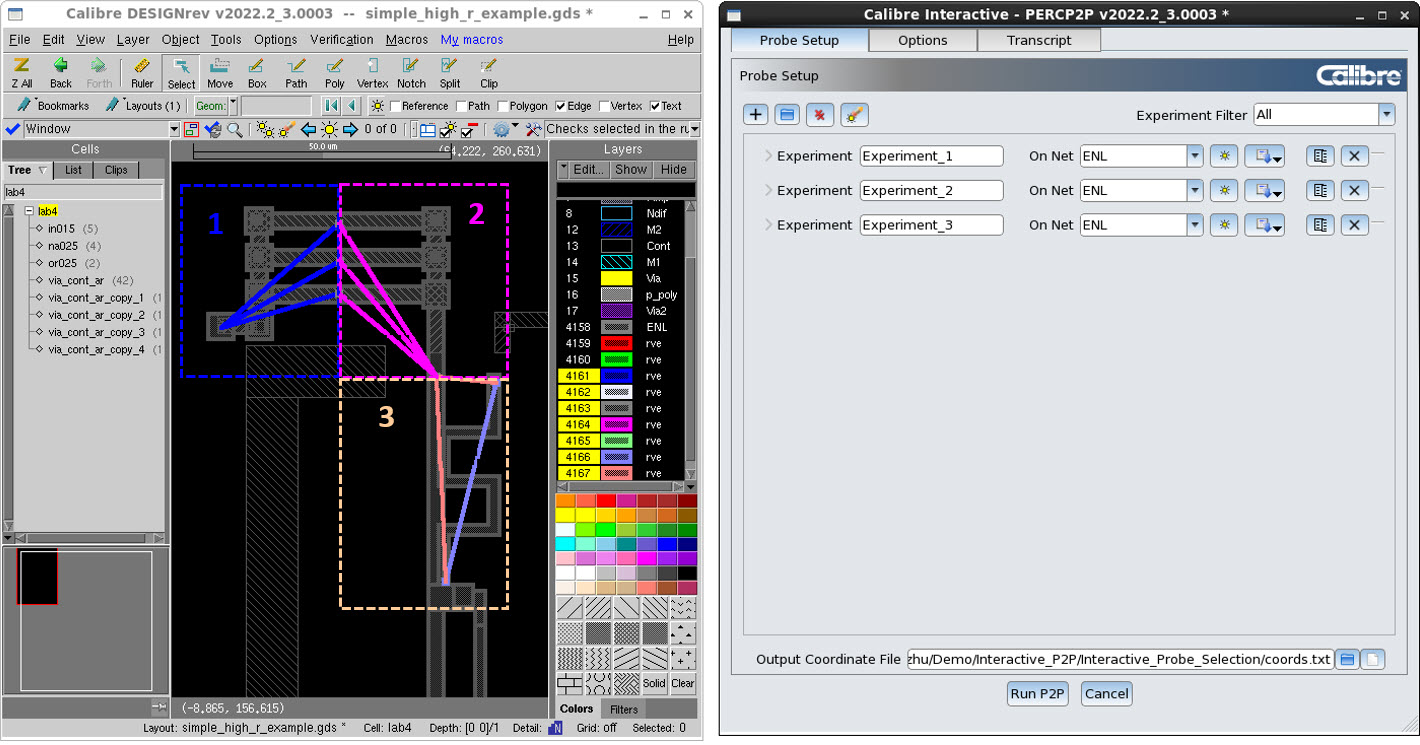

加利福尼亚州圣何塞4月6日消息——Cadence Design Systems, Inc.(纳斯达克代码:CDNS)今天宣布了Cadence®Palladium®Z2企业仿真和Protium™X2企业原型系统,以应对指数级增长的系统设计复杂性和上市时间压力。基于Cadence目前业界领先的Palladium Z1仿真和Protium X1原型平台,这些下一代系统能够为业界最大的数十亿门系统级芯片(SoC)设计提供最高吞吐量的硅前硬件调试和硅前软件验证。由于其与统一编译器和接口的紧密集成,Cadence被称为“动态组合”,这些系统中的下一代仿真处理器和Xilinx UltraScale+ VU19P fpga为客户提供了2倍的容量和1.5倍的性能改进,使Cadence客户能够在更短的时间内在更大的芯片上运行更多的验证周期。此外,这两个系统都提供了突破性的模块化编译技术,能够在Palladium Z2系统上在10小时内编译100亿个门,在Protium X2系统上在24小时内编译。

NVIDIA公司硬件工程高级总监Narendra Konda表示:“我们的高端图形和超大尺寸设计的复杂性每一代都在增加,而我们的上市时间安排也越来越紧。”“使用Cadence Palladium Z2和Protium X2系统的通用前端流程,我们正在优化验证、验证和前置硅软件开发之间的工作负载分配。由于可用容量增加了两倍,吞吐量提高了50%,模块化编译器的周转速度更快,我们可以全面和按时验证我们最复杂的GPU和SoC设计。”

Palladium Z2 / Protium X2动态组合旨在解决那些为最先进的应用程序设计所面临的挑战,包括移动、消费和超大规模计算设计。通过无缝集成的流程、统一的调试、通用的虚拟和物理接口以及跨系统的测试平台内容,动态组合提供了从仿真到原型的快速设计迁移和测试。

“AMD成功的一个重要部分是加速我们的产品开发过程,优化我们的左移战略,”AMD公司研究员、方法论架构师Alex Starr说。“随着Cadence Palladium Z2和Protium X2系统性能的提高,我们可以提高硅前工作负载吞吐量,同时保持仿真和原型之间的功能一致性。在短时间内完成Palladium Z2仿真和Protium X2原型平台之间的设计启动和转换的能力,为我们提供了优化我们最具挑战性的SoC设计的左移部署的机会。凭借使用行业领先的第三代AMD EPYC™处理器以及Palladium Z2和Protium X2平台的服务器资格,客户将能够为Palladium和Protium生态系统带来行业领先的性能计算。”

Cadence高级副总裁兼系统与验证组总经理Paul Cunningham表示:“先进SoC设计的硅前验证需要具有数十亿门容量的解决方案,既能提供最高性能,又能提供快速可预测的调试。”“我们新的动态组合通过两个紧密集成的系统满足了这些要求,Palladium Z2仿真优化用于快速可预测的硬件调试,Protium X2原型优化用于最高性能的数十亿门软件验证。我们对客户的强烈兴趣感到兴奋,并期待着与他们合作,利用这些新系统来实现其设计的最高验证吞吐量。”

Arm设计服务高级总监Tran Nguyen表示:“一流的仿真是我们成功的关键,Arm广泛使用仿真以及基于Arm的服务器上的仿真,以实现最高的验证吞吐量。”“凭借新的Cadence Palladium Z2系统,我们最新设计的性能提高了50%,容量提高了2倍,为我们提供了验证下一代IP和产品所需的强大的pre-silicon功能。”

Xilinx公司核心垂直市场高级总监Hanneke Krekels表示:“Xilinx和Cadence密切合作,确保Cadence软件前端与Xilinx Vivado Design Suite后端无缝工作,实现最佳性能和容量效益。Cadence Protium X2企业原型系统旨在使用我们的Virtex UltraScale+ VU19P设备为数十亿门设计提供多mhz性能。紧密集成的Cadence和Xilinx前后流程允许软件开发人员在开发流程的最早时间点使用该平台,并专注于设计验证和软件开发,而不是原型开发。”

Cadence验证全流程,包括Palladium Z2仿真、Protium X2原型、Xcelium™逻辑仿真、JasperGold®形式化验证平台和Cadence智能验证应用程序套件,提供最高的每天每美元的错误验证吞吐量。新的Palladium Z2和Protium X2系统是更广泛的Cadence验证套件的一部分,支持公司的智能系统设计™战略,实现卓越的SoC设计。Palladium Z2和Protium X2系统已在部分客户部署,将于2021年第二季度全面上市。有关Palladium Z2和Protium X2动态duo的更多信息,请访问http://www.cadence.com/go/

关于节奏

Cadence是电子设计领域的关键领导者,拥有30多年的计算软件专业知识。该公司应用其底层智能系统设计策略,提供软件、硬件和IP,将设计概念变为现实。Cadence的客户是世界上最具创新精神的公司,为最具活力的市场应用提供从芯片到电路板到系统的卓越电子产品,包括消费、超大规模计算、5G通信、汽车、移动、航空航天、工业和医疗保健。《财富》杂志连续六年将Cadence评为最适合工作的100家公司之一。欲知详情,请浏览cadence.com.