结果是:Optima声称将功能安全故障覆盖率提高了1000倍,使大型ASIL-D芯片成为可能。

功能安全是新出现的令人头疼的问题。曾经只有航空设计才有,现在汽车把它推到了聚光灯下。我们已经讨论过了之前,但是大部分的讨论,也许并不总是明确说明,对低asil设计有实际的影响,也就是说,对不太安全的组件。我们从来没有直接解决过ASIL-D——应用于发动机控制和制动等方面的最高级别的问题。

但是和新发布Optima将ASIL-D带到了前台。ASIL-D要求对超过99%的故障覆盖率进行分析,但对于大型芯片来说,这种分析花费的时间太长,这意味着只有小芯片——主要采用180纳米工艺(单事件故障限制在90纳米,或seu)——才有资格获得ASIL-D评级。

他们说每个门必须模拟6次(卡在1/0在2个输入和一个输出)。举个例子,一个有1亿个门的中小型芯片,每次运行1分钟进行模拟,需要6亿分钟,也就是一千多年的时间来分析。这可能会打破上市时间窗口。因此,要么需要进行仿真(多个仿真器并行运行——非常昂贵!),要么对设计进行采样,而不是详尽地分析。根据定义,使用这种方法,您无法获得99%的故障覆盖率。

擎天柱出名的根本原因是他们的新的FIE(故障注入引擎)工具集,这将这个过程加快到仅仅一年多的例子设计-在单核上。然后,您可以使用并行性将其带入范围内,现在您有了生产更大ASIL-D芯片的途径。

他们通过从头开始重做算法,利用模拟和形式分析的结合来做到这一点。他们提出了新的故障修剪和故障崩溃技术,可以在硬计算开始之前减小问题的规模。它们既可以在RTL级别上运行,在RTL级别上您可以进行评估,也可以在netlist级别上进行最终的检查。

电路分类

在我们讨论这些工具的作用之前,看看不同类别的可能故障是有指导意义的,因为如果您是安全游戏的新手,其中一些并不明显。这里的想法是,最终,你将有你的主电路逻辑,然后你将有安全机制,当故障发生时,检测故障。Optima有一张他们使用的图,他们很友好地将其分解以帮助说明概念。

主逻辑具有影响锥(CoI):这是所有有助于输出的逻辑。把它想象成一个分水岭,由最终汇入一条特定河流的所有溪流和小溪定义。下面显示的是这个CoI。

(图片由Optima提供)

这里有两点需要注意。首先,输出被隐晦地称为“故障频闪”。我发现这令人困惑,因为在应用程序中,这些并不是在发生故障时激活的频闪。它们是信号可以如果他们失败了,就会产生安全问题。Optima建议将它们视为“关键信号”。根据定义,如果这些信号没有受到安全机制的保护,它们就被认为是不安全的。CoI周围的绿色代表其他逻辑-逻辑不是安全问题,所以它都是安全的-根据定义。

上图假设没有安全电路;接下来我们把它们放进去。它们也有一个CoI,如下所示。Optima是指安全电路的输出为检测用闪光灯,因为它们将指示是否检测到故障。也就是说,一些安全电路没有输出——事实上,一些正确的错误。在这种情况下,错误不会传播到输出,因为它已被纠正。

(图片由Optima提供)

这幅图还说明了另一个概念:可见性。在此上下文中,可见故障是指可以由安全机制检测到的故障。这表明,根据定义-几乎-安全电路是可见的。我说“几乎”是因为,事实上,安全电路也可能有故障,你可能想要检测它们,所以这里可能有点像剥洋葱,用安全机制来检测主要逻辑问题,更多的机制来检测安全机制问题,还有更多的机制……这是渐进的,但无论如何你都不可能达到100%的覆盖率,真的,所以你只需要达到99%以上的水平

现在我们在同一个芯片上有两个coi,事实上,它们是重叠的。它们不可能完全重合,因为安全机制将涉及一些不属于主CoI的电路,并且可能有一些主CoI没有被覆盖。安全CoI中不重叠的部分被认为是安全的,因此它们被标记为安全的可见.然而,主要CoI的非重叠部分表示不安全的看不见的逻辑上,你想要最小化这个空间。

重叠的区域是由安全机制覆盖的逻辑,所以它是不可见的这意味着它们是关键电路,如果出现故障,可能会导致问题,但现在任何故障都是可见的,因为它与安全CoI相交。

(图片由Optima提供)

剩下的问题是,这个区域内的断层是否真的被探测到了。这为分析提供了两个主要步骤:首先,使用静态分析和形式化技术来建立coi和重叠区域。第二步是证明重叠区域的安全电路可以检测到99%的可能故障。这是故障注入和模拟的工作。

显然,FMEDA(游戏邦注:即失败模式、效果和诊断分析)世界中存在一些与这些区域相关的艺术术语,而Optima则提供了一张“地图”。

(图片由Optima提供)

在故障分析之后,您最终会得到由安全电路检测到的故障和未检测到的残余故障组成的子区域。检测区域必须大于99%。

(图片由Optima提供)

三件工具在箱子里

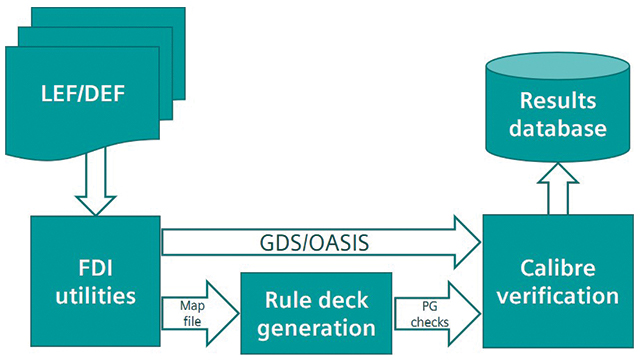

Optima FIE由三个工具组成:一个用于识别coi的初始分析,一个用于处理硬错误,一个用于处理软错误。

(图片由Optima提供)

让我们先回顾一下硬错误和软错误。硬错误指的是一种永久性的情况:信号卡在1或0。(桥接也是一种可能的情况,但根据Optima的说法,目前还没有人能做到这一点;这在他们的路线图上。)有一件事很容易让人感到困惑,那就是这些错误是如何从一开始就逃过测试的。为什么有卡在缺陷的芯片没有被拒绝?

因为我们这里讨论的不是制造故障;我们讨论的是出现的错误后在系统中安装了一个好的芯片。也许是电压故障,或者是环境因素的问题。因此,我们的假设是,这个错误仍然存在。分析问题是,“如果出现这样的错误,它会有明显的影响吗?”这就是故障注入的全部内容:用故障节点替换已知的良好节点,并查看是否检测到故障。

然后是软(或瞬态)错误:这些是系统中由于某种原因(α粒子或其他seu)受到干扰的信号,这些信号可以恢复,即使只是通过电源循环。虽然硬错误可能会导致系统永久无法使用(挑战在于如何安全地关闭系统),但软错误可能是可以接受的——如果它发生时可以检测到的话。这种检测(但不是校正)可以通过所谓的双核lockstep冗余(也称为双模冗余,或DMR).如果下面的主回路和影子回路不一致,那就表明出了问题。

(图片由Optima提供)

软错误甚至可以使用三模块冗余(TMR)来纠正,尽管这需要更多的硅,使其更加昂贵。

(图片由Optima提供)

DMR可以涵盖的范围是一个需要讨论的问题。通常,它用于CPU和相关逻辑——换句话说,一个大块。这是因为它创建了一个必须以某种方式路由的检测输出。另一方面,TMR可以更容易地在寄存器级使用,因为它没有输出;它修正了信号。

在与Arteris关于CodaCache IP的单独讨论中,他们提到他们在低于CPU级别的级别上使用DMR(因为它不是CPU电路)。但它们不会一直到收银台。路由检测频闪的问题是如何在芯片上进行通信的问题。如果您使用的是片上网络(NoC),则电路可能会在网络上启动检测消息,这意味着不需要在芯片上路由额外的信号。或者,在性能允许的情况下,理论上可以在有线或配置中将单个检测频闪连接到所有检测器。这仍然可能造成负担(特别是如果您必须为了性能而分割线),所以这里的要点是,设计师必须仔细考虑DMR的范围。

Optima FIE Flow

我们使用这三个工具并按顺序运行它们,从Optima-SA开始,它创建一个最小的故障列表。这是现有类似工具的标准功能,尽管与其他工具相比,Optima-SA在进行故障修剪和崩溃方面可能存在一些差异。擎天柱的版本运行不到一个小时。

与现有工具的主要区别在于对硬错误和软错误列表所做的后续分析。Optima-HE分析芯片,以确保安全机制提供足够的覆盖范围,这是向ISO-26262大师证明覆盖范围足以达到ASIL-D等级的必要步骤。如果覆盖率太低,他们的coveragemmaximizer工具会提供关于如何改进它的建议。

与此同时,Optima-SE分析所有的触发器,以确定需要“加固”的地方。硬化可以像使触发器更耐亚稳一样简单,也可以像TMR一样昂贵。任何硬化都有一定的代价,所以您希望将硬化限制在尽可能少的情况下。Optima-SE通过计算每个触发器的架构脆弱性因子(AVF)来帮助解决这个问题。这相当于自己计算出触发器的失败率(FiT)。从这里开始,您可以计算如果高avr的人字拖被硬化,将导致的总体FiT率。Optima表示,在Optima- se之前,这些计算需要几个月的时间。

该工具不会自动插入硬化回路;实现这些变化仍然取决于设计师。该工具的好处是识别出最小的一组人字拖——那些影响最大的人。这样就可以进行更多的手术修复。但是,请注意,DMR在这里是不太可能的解决方案,因为它在触发器级别操作,而DMR通常不会在那么低的电平上使用。

一些Optima的资料显示-SA先运行,然后是-HE,然后是-SE,按照特定的顺序。虽然-SA确实必须先运行,但其他两个可以按任意顺序运行。显然,历史上有这样的倾向-他先做,但这绝不是必须的。

在对安全概念进行了所有这些讨论之后,可能有必要再次退出来提醒自己这里有什么新内容。从理论上讲,这样做的好处是众所周知的。问题在于运行分析所需的时间。因此,抛开每种工具如何工作的细节不谈,这里的根本变化是分析时间的显著改善,提高了芯片的复杂性,这些芯片可以被整合到安全关键设计中,而不会损害安全性。

更多信息:

采购来源:

Jamil Mazzawi, Optima创始人兼首席执行官

如果你能得到一个符合ASIL-D标准的大型汽车SoC,你会做什么?

我将非常乐意回答关于文章和Optima安全平台的任何问题。

就在下面留言吧