结果:最适条件声称1000 x加速functional-safety故障覆盖率,使可能的大ASIL-D芯片。

功能安全新头痛。一旦留给mil /航空设计,汽车已经推到聚光灯下。我们已经讨论过它之前,但是大部分的讨论,也许并不总是明确,有实际影响主要用于lower-ASIL设计——也就是说,安全性至关重要的组件。我们从来没有解决ASIL-D——最高水平,应用于发动机控制和刹车——直接。

但是谈话新发布最适条件带来了ASIL-D前面和中心。文档的分析需要大于99%的故障覆盖率——ASIL-D所需仅仅花费的时间太长大型芯片,这意味着只有小芯片——大多在180 nm流程(和限制为单事件令90海里,或建)——获得ASIL-D评级。

他们说,每个门都必须模拟6倍(停留在输入和输出2日1/0)。作为一个例子,一个中小芯片1亿门,模拟每跑1分钟,需要6亿分钟,或略高于一千年,来分析。这可能打破了上市时间窗口。结果,模拟是必需的(并行运行多个模拟器——贵!)或设计采样而不是详尽的分析。使用这种方法,你不能得到99%的故障覆盖率,通过定义。

最适条件的根本出名是他们新五(错误注射引擎)工具集加速这个过程,就在一年多的例子——在一个核心设计。然后您可以使用并行性将其范围内,现在你有途径生产大ASIL-D芯片。

他们这样做的重建算法,利用模拟和形式分析的结合。他们声称新的fault-pruning和fault-collapsing技术,降低问题的规模很难计算开始前。他们可以在RTL级,你可以估计,并为最终检验在网表级。

电路分类

之前进入的工具做什么,看起来非常有意义在不同类别的可能的故障,因为这不是显而易见的,如果你的一些新的安全游戏。这里的想法是,最终,你将会有你的主电路的逻辑,然后你要有安全机制,检测故障发生时。他们使用最适条件有一个图纸,他们友善帮助说明的概念将其分解。

影响的主要逻辑有一个锥(CoI):这是所有的逻辑,有助于一个输出。认为它是一个分水岭,定义为所有的河流和小溪,最终融入到一个特定的河流。这CoI见下。

(图片由最佳状态)

这里有两件事需要注意。首先,输出是隐秘地称为“失败闪光灯。“我发现令人困惑,因为,在应用程序中,这些不是闪光灯,激活发生故障时。他们的信号可以失败,如果他们这么做,它将创建一个安全问题。最适条件建议考虑“关键信号。”的定义,然后,这些信号被认为是不安全的,如果他们不受安全保护机制。周围的绿色CoI代表其他逻辑,逻辑不是一个安全问题,这是所有安全——根据定义。

上图假定没有安全电路;接下来,我们将把这些。他们也有硬币,显示下一个。最适条件是指安全电路的输出检测用闪光灯失败,因为他们将指示是否已被检测到。也就是说,一些安全电路没有输出——事实上,一些正确的错误。在这种情况下,错误不会传播到输出,因为它是被修正。

(图片由最佳状态)

这幅图也说明了另一个概念:可见性。在这种背景下,一个明显的错误是可以检测到一个安全机制。这表明,通过定义——几乎是可见的安全电路。我说,“几乎”,因为,事实上,安全电路也可以有错误,你可能想要检测,这里可能有一些洋葱剥皮,安全机制来检测主逻辑问题,更多的检测机制,安全机制问题,和更多的机制对于那些…这是渐近,但不管怎么说,你永远不会达到100%的覆盖率,真的,所以你只需要得到高于99%的水平

现在我们有两个coi在同一芯片,,事实上,他们重叠。没有他们会完全一致,因为安全机制将涉及一些电路主要CoI的一部分,不可能有主要CoI的不算在内。重叠的部分安全CoI被认为是安全的,所以他们指出安全的可见。然而,重叠部分的主要CoI代表不安全的看不见的逻辑,你想减少空间。

重叠的区域是由逻辑安全机制,所以它的不可见的,这意味着他们关键电路可能会导致一个问题如果有错,但现在任何缺点都是可见的,因为它与安全CoI相交。

(图片由最佳状态)

剩下的问题是是否真正发现错误在这个地区。使两个主要步骤的分析:首先,静态分析和正式的技术用于建立coi和重叠区域。第二步是证明重叠区域的安全电路可以检测> 99%的可能的错误。这是一个故障注入和仿真的工作。

显然有一些艺术方面的FMEDA(失效模式、效果和诊断分析)的世界,与这些地区,和最适条件提供了一个“地图”。

(图片由最佳状态)

故障分析后,最后一个次区域检测到的故障安全电路和残留的缺点,还没有被发现。检测区域必须在99%以上。

(图片由最佳状态)

三个工具的胸部

最适条件5包含三个工具:一个用于标识coi的初步分析,一个用于处理硬错误,一个用于处理软错误。

(图片由最佳状态)

我们首先回顾一下困难的——与软件出错的事情。硬错误指的是一个永久的条件:信号在1或0。(桥接也是一个可能的条件,但是,根据最适条件,没有一个能够覆盖;在他们的路线图。)很容易感到困惑的一件事是此类错误如何逃脱了测试放在第一位。为什么没有芯片与停留在错误拒绝吗?

因为我们在这里讨论的不是制造错误;我们讨论故障出现后一个好的芯片已被安装在一个系统。也许有一个电压故障,或者与一些环境因素有一个问题。的假设,然后,故障依然存在。和分析的问题是,“如果这样一个故障出现,会有明显效果吗?“这就是错误注射的是:替换一个已知良好的节点与一个错误的节点和看到,如果检测到故障。

还有软(或瞬态)错误:这些系统中信号得到摄动出于某种原因-阿尔法粒子或其他建可以恢复,即使只是通过一个动力循环。虽然硬错误可能导致系统永久不可用(所面临的挑战是把系统安全),软错误可能适应——如果它可以发现当它发生。这样的检测(但不是修正)可以通过所谓的双核发生(也称为同步冗余双模冗余,或DMR)。如果下面的大师和影子电路不同意,那就表明的东西是错误的。

(图片由最佳状态)

软错误甚至可以纠正使用三冗余(咯),尽管使用更多的硅,使它更昂贵。

(图片由最佳状态)

的范围可以覆盖DMR的一些讨论。经典,它用于CPU和相关的逻辑——换句话说,一大块。那是因为它创建了一个检测输出路由了。咯,另一方面,可以在注册级别更容易使用,因为它没有输出;它纠正了信号。

在一个单独的讨论和Arteris就CodaCache IP,他们提到他们使用DMR水平低于CPU水平(因为它不是一个CPU电路)。但是他们不走一直到寄存器的水平。路由发现闪光灯的问题是如何通信发生在一个芯片。如果你使用network-on-chip (NoC),电路可能会发起一个检测消息网络上的,也就是说,没有额外的路由整个芯片的信号。或者,理论上性能允许的话,你可以有一个检测闪光灯连接到探测器在一个有线或配置。仍然可以创建一个负担(特别是如果你有段线的性能),所以主要的点,DMR的范围由设计师必须仔细考虑。

最适条件5流

我们把三个工具和运行它们,从Optima-SA,创建一个最小的错误列表。这是一个标准功能类似的工具可用,虽然可能会有一些差异基于Optima-SA确实错修剪和崩溃相比其他工具。最适条件的版本运行在不到一个小时。

从现有工具的主要差异来自后续分析完成,硬实力和软错误列表。Optima-HE分析芯片,确保安全机制提供足够的覆盖率——证明的必要步骤的iso - 26262大师报道足以达到一个ASIL-D评级。如果覆盖率太低,他们CoverageMaximizer工具提供建议如何改进它。

Optima-SE,与此同时,分析所有的人字拖,确定“硬化”是必需的。淬火可以简单到一个触发器对亚稳态或贵咯。任何硬化有一定的成本,所以要限制硬化尽可能少的人字拖。Optima-SE有助于通过计算架构弱点因素,或动静脉,每个触发器。这相当于找出failure-in-time(合适)的触发器。从这里,你可以计算的整体配合率结果如果high-AVR拖鞋硬化。最适条件说,Optima-SE之前,这些计算需要好几个月。

该工具不自动插入淬火电路;它仍然是由设计师来实现变化。工具的好处是确定一组最小的拖鞋——那些拥有最影响。,允许更多的手术修复。但是请注意,DMR是一个不太可能的解决方案,因为这个触发器的操作水平,DMR不是通常使用低水平。

最适条件的一些资料显示股价运行第一,然后他,然后硒,在那个特定的顺序。而sa确实必须先运行,另外两个可以运行在秩序。显然,有一个历史先做他的倾向,但这决不是必需的。

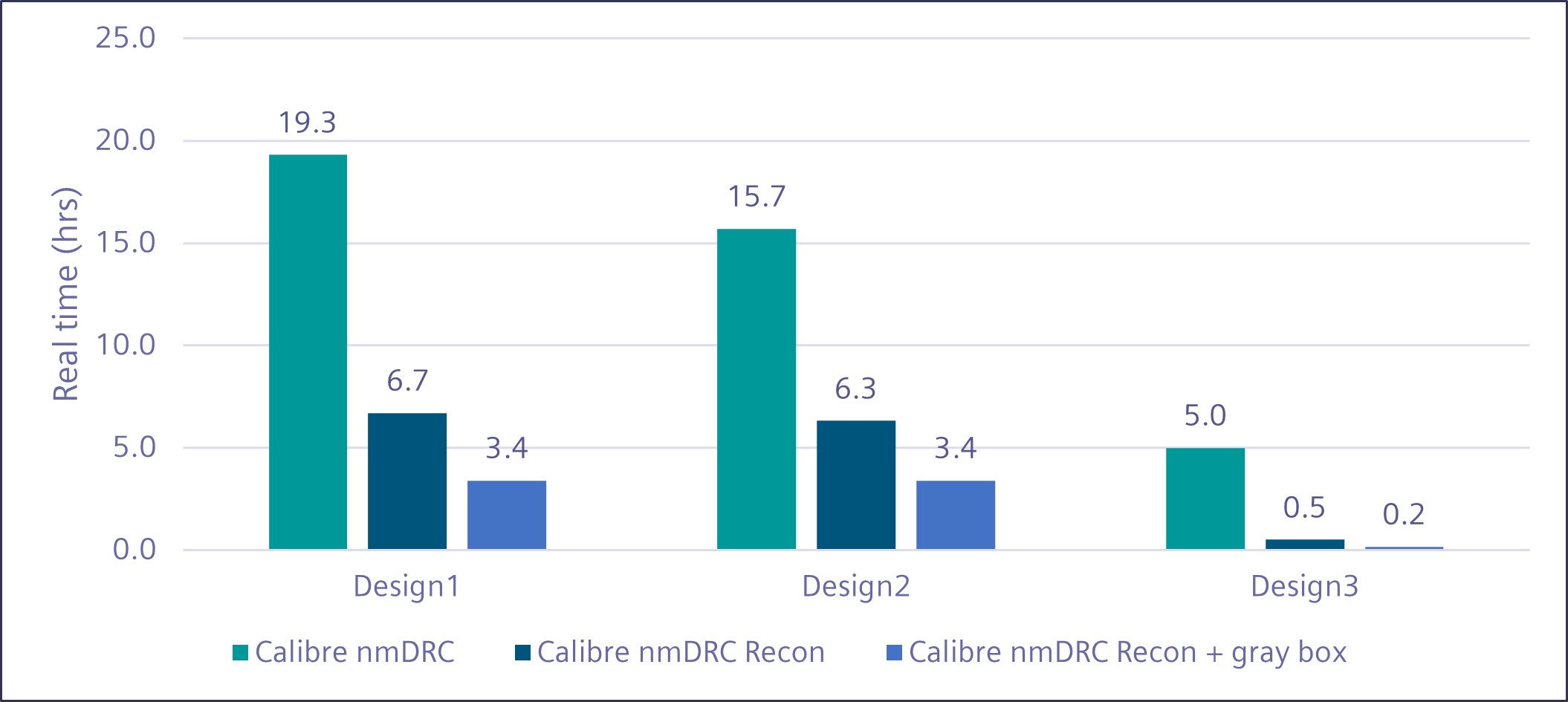

毕竟这个讨论的安全概念,它可能是有用的退出再次提醒自己有什么新鲜事。做所有的这些理论的好处是众所周知的。问题是时间运行分析。所以,除了每个工具如何工作的细节,这里的根本变化是显著改善分析时间,提高芯片的复杂性可以被纳入安全性至关重要的设计在不影响安全。

更多信息:

采购来源:

创始人兼首席执行官,贾米尔Mazzawi最适条件

你建立如果你能得到一个大型汽车SoC ASIL-D资格吗?

我将很高兴回答任何关于文章的问题和最适条件的安全平台。

把问题作为一个风箱置评