Microchip在上个月的RISC-V峰会上预览了其PolarFire 2中端SoC FPGA家族,其中包括该公司FPGA业务副总裁Bruce Weyer的主题演讲。尽管该公司提供的产品细节很少,但它给出了很多暗示。如此多的提示,事实上,我可以给你我根据这些提示收集的信息,告诉你我的想法,让你得出自己的结论。我会给你2,让你检查我的数学,但你需要自己把2加起来,得到4。我们将在6个月左右的时间里,在Microchip的RISC-V生态系统合作伙伴的PolarFire SoC fpga的Mi-V会议上,看看我们的预测是否正确。

最初的PolarFire SoC FPGA家族首次出现在2017年,然后Microchip在2019年宣布了具有强化RISC-V微处理器内核的SoC版本。(参见“Microchip PolarFire采用RISC (-V)) PolarFire是一个中端FPGA家族,具有25K至460K逻辑元件(LEs)和12.7 Gbps SerDes收发器,完全属于中端FPGA类别。

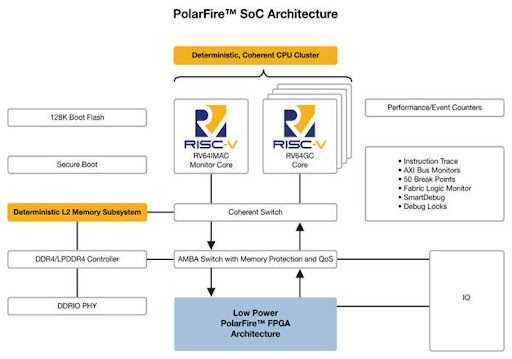

最初的PolarFire家族的SoC成员包含一个多核微处理器子系统,由一个SiFive E51 RISC-V处理器核心和四个SiFive U51 RISC-V处理器核心组成,所有这些都通过相干总线开关连接到片上2兆字节的L2缓存存储器。PolarFire SoC的可编程逻辑结构通过连接到相干总线交换机的AMBA交换机,通过多个64位AXI4接口端口连接到处理器核心。到目前为止,我们还不知道PolarFire 2 SoC的微处理器子系统是什么样子的,但图1显示了最初的PolarFire SoC的微处理器复杂性的框图。PolarFire 2 SoC的微处理器子系统无疑会更大更好。

图1:最初的PolarFire家族的SoC成员包含一个多核微处理器子系统,由一个SiFive E51 RISC-V处理器核心和四个SiFive U51 RISC-V处理器核心组成。图片来源:Microchip

用于制造PolarFire FPGA和soc的半导体制造工艺的SONOS变体提供了原始PolarFire FPGA织物用于其配置内存的非易失性内存能力。由于与AMD/Xilinx和英特尔的中端fpga和soc一样,PolarFire soc使用非易失性SONOS内存SRAM单元作为配置内存,因此它们对辐射诱导的seu(单事件扰动)免疫,这使它们成为航天器中使用的首选fpga。现在太阳系里到处都是极火型的soc。至少有一架PolarFire SoC在NASA最近的猎户座1号太空任务中环绕月球飞行。

我们还不知道Microchip将使用什么工艺技术来制造PolarFire 2 FPGA和soc,但在其PolarFire 2家族的预览中,Microchip声称它将使FPGA织物的电源效率翻倍,同时织物的性能也翻倍。PolarFire 2 FPGA织物将再次具有像最初的PolarFire家族一样的SEU免疫,它将具有“军用级”防篡改和网络安全功能。该公司还声称,相对于最初的PolarFire系列,它将使PolarFire 2 soc上计算元件的CoreMark基准性能提高两倍,并将最大TOPS性能提高15倍。该公司承诺将在今年晚些时候的Mi-V峰会上公布更多细节。Mi-V是Microchip的RISC-V生态系统。以上就是Microchip关于新PolarFire 2系列的全部介绍。

一种新的工艺技术

虽然Microchip没有提供关于Polarfire 2家族的很多细节,但它确实提供了很多直接和间接的线索。正如我在本文开头所建议的,我不能向您保证我的算术是正确的,所以我邀请您自己将这些线索加起来。

让我们从工艺技术开始。我在谷歌上快速搜索了一下,找到了一份名为“PolarFire非易失性FPGA系列提供了突破性的价值:成本优化,最低功耗,SEU抗扰性和高安全性,描述了联华电子如何使用平面28纳米SONOS(硅-氧化物-氮化物-氧化物-硅)工艺技术为Microchip制造最初的PolarFire器件。SONOS是一种工艺技术,通过在FET的栅极中插入一层薄薄的氮化硅电荷捕获层,将非易失性存储器添加到芯片中。电荷捕获层作为存储器,具有两种状态:带负电荷和带正电荷(耗尽电子,产生空穴)。电子可以通过福勒-诺德海姆隧穿现象进出这一层。SONOS半导体工艺自20世纪70年代末就已经出现。

将PolarFire 2器件的FPGA结构的功率效率和性能提高一倍意味着Microchip将需要使用更高级的处理节点。任何比28nm更先进的节点都很可能使用finfet而不是平面fet。UMC是Microchip目前的FPGA芯片代工公司,拥有14nm FinFET工艺技术,承诺比其平面28nm工艺降低50%的功耗。然而,在UMC的网站上,关于14nm工艺的信息相对较少,因此无法判断该工艺技术是否具有生产PolarFire 2芯片所需的非易失性存储器能力。

再谷歌一下,我就知道自2005年以来,我们已经知道可以使用SONOS工艺步骤在finfet(而不是平面fet)中添加电荷捕获层,这要感谢台积电的几位作者,他们在当年华盛顿特区举行的IEEE国际电子器件会议上发表了一篇关于该主题的论文。然而,这些线索证明不了什么。微芯可能甚至不打算使用UMC来制造PolarFire 2芯片,所以你必须把两件事放在一起来决定微芯将使用什么样的工艺技术来制造PolarFire 2设备。我们甚至不知道Microchip是否会使用非易失性SONOS finfet作为配置内存,但最初的PolarFire家族的SONOS配置内存已经成功了,所以为什么不呢?

我认为该公司更有可能坚持使用SONOS非易失性存储单元,而不是一些更新奇的东西,如电阻RAM或磁性RAM,因为NASA喷气推进实验室(NASA喷气推进实验室)去年8月宣布,它已经选择与Microchip在密切相关的HPSC(高性能航天计算)项目上合作。Microchip已经有大量的fpga、soc和其他太空部件在太空中飞行,所以NASA JPL选择Microchip设计和制造HPSC也就不足为奇了,这是NASA JPL试图为所有未来的太空项目采用一个标准化的多核计算平台,并将现有的以太空为中心的计算性能提高至少100倍。JPL希望为其HPSC处理器开发一个全球生态系统,并希望利用熟悉特定处理器架构的大量程序员。

根据Weyer的主题演讲,这一选择至少会间接影响PolarFire 2微处理器子系统的外观,因为他表示,PolarFire 2 SoC FPGA将具有兼容hpsc的核心复合物,因此PolarFire 2 FPGA SoC家族的版本也可以用于太空应用。因为这是NASA的一个项目,而且NASA喜欢搭载已经飞行过的硬件,像MRAM和RRAM这样的非易失性存储器不太可能出现在飞往太空的新芯片上。至少在不久的将来不会。

虽然Microchip没有提供关于PolarFire 2 SoC fpga微处理器子系统的直接信息,但该公司在不同的地方隐藏了线索。根据SiFive于2022年9月6日发布的新闻稿,HPSC芯片将利用SiFive的8个64位X280 RISC-V处理器内核和512位矢量扩展,以及SiFive的4个额外的RISC-V内核。SiFive X280处理器核心还包含了SiFive所谓的“智能扩展”,这是SiFive开发的用于加速AI/ML操作的自定义指令。

Weyer并没有明确表示,PolarFire 2 SoC FPGA的微处理器子系统将基于8个SiFive X280处理器核心,另外还有4个SiFive核心将在晚些时候命名,就像HPSC一样,但他在主题演讲中指出:

- Microchip自2015年以来一直与SiFive合作

- 该公司在其FPGA库中提供三个RISC-V软核

- 现有的PolarFire SoC fpga包含一个SiFive E51和四个SiFive U54处理器核心

- PolarFire 2 SoC fpga中使用的微处理器子系统将与HPSC处理器ASIC“兼容”

再说一次,你可以做数学计算,但我认为很明显Microchip将在PolarFire SoC FPGA中采用微处理器子系统。它可能拥有和HPSC一样多的SiFive处理器核心实例,也可能没有。我们还不知道。

一般的安全

最后,Microchip的Weyer提到,PolarFire 2设备将包含“军事级别的安全”。如今,这种说法强烈地暗示了后量子密码学的存在,特别是对于注定要在30年内可用并设计用于该领域几十年的新设备。我非常期待像IBM这样的公司到那时将拥有可用于商业用途的量子计算机。后量子密码学目前处于不断变化之中。NIST(美国国家标准与技术研究所)正在进行一项基于后量子密码学的开发、认证和采用新的安全标准的计划。(有关更多信息,请参阅“迫在眉睫的加密危机随着量子计算而来”)。

虽然微芯片没有提供更多关于军事级安全的细节,但我在RISC-V峰会上与PQShield的工程副总裁格雷姆·希基(Graeme Hickey)的另一次谈话表明了微芯片可能采取的一个方向。PQShield是一家初创公司,由英国牛津大学的一群加密研究人员组建。2022年6月1日,PQShield宣布Microchip授权其后量子密码学IP核“在未来几年用于其产品组合”。根据Hickey的说法,PQShield的后量子加密软件库支持所有NIST候选的基于晶格的量子安全加密方案,包括Kyber、Dilithium和Falcon。PQShield的硬件IP实现目前支持Kyber和dlithium,并集成了对侧通道攻击的保护。

我特别向希基询问了基于晶格的量子安全加密方案,因为最近有两个人用笔记本电脑破解了NIST的另一个候选方案SIKE(超奇异异构密钥封装,发音为“叹气密钥”)。比利时鲁汶天主教大学的Thomas Decru和Wouter Castryck在一两天内就打破了这个基于数学家恩斯特卡尼1997年发表的定理的计划。至少现在是这样。

为了更好地了解后量子密码学的现状,我联系了IBM研究院苏黎世中心的工作人员西尔维奥·德拉贡(Silvio Dragone)。Dragone发表了一篇博客我们如何对IBM z16进行量子防护这篇文章去年10月出现在IBM的网站上。IBM zSystem大型机长期以来合并了称为硬件安全模块(HSM)的加密协处理器卡,IBM z16大型机的HSM包含实现crystaldilithium和Kyber后量子加密算法候选算法的硬件。

Dragone解释说,IBM选择使用Dilithium和Kyber算法的硬件实现来加速z16大型机的HSM,该算法基于IBM在苏黎世完成的后量子密码学研究。该研究基于一个经过充分研究的数学问题,并表明这些算法在大型机环境中提供了最佳性能。他说,NIST的后量子竞赛的美妙之处在于,它允许全世界的密码专家分析这些算法,以梳理出任何缺陷。这就是SIKE的情况。

Microchip还没有宣布在其PolarFire 2设备的背景下,“军事级安全”意味着什么,但我提供了我在RISC-V峰会上收集到的线索。再一次,我建议你自己算算。

最终的中档FPGA统计

在RISC-V峰会上,Microchip声称,最初的PolarFire fpga的功耗是竞争对手中端fpga的“两倍”,而PolarFire 2设备的效率将再次翻倍。当工具和芯片可用时,您需要自己评估这个声明。我的经验告诉我,功耗很大程度上取决于在FPGA中实例化的设计。然而,Microchip还没有描述PolarFire 2设备,更不用说制造它们了,所以PolarFire 2必须进入未来fpga的虚无范畴,以及几个还没有建成的更新的中端fpga。这一类别包括英特尔最近宣布的Agilex d系列和Sundance Mesa fpga和soc,计划使用英特尔7工艺制造。这是以前被称为10nm增强型superin的工艺,10nm superin++之类的;它已经改变了几次。(参见“英特尔推出两个单片Agilex FPGA和SoC系列"和"英特尔欢迎您进入埃斯特姆时代”)。

在未来中端FPGA的另一场竞赛中,Lattice Semiconductor最近公布了其基于台积电16nm FinFET工艺技术的中端Avant FPGA平台,以及基于Avant平台的第一个系列,称为Avant- e。莱迪思的Avant将使用Avant平台生成多个中端FPGA系列。(参见“ag亚博只为非凡 ”)。

老实说,在未来的中端FPGA类别中,它会变得非常拥挤,这对未来的FPGA设计来说是一个好消息,但很难将尚未出现的FPGA进行比较。然而,如果你看看Microchip的PolarFire 2预览公告收集的线索,你就会明白为什么我期待Microchip在今年晚些时候正式推出新的中档FPGA和SoC家族。具有如此强大的片上微处理器火力的可编程逻辑部件,再加上片上、非易失性FPGA配置内存和较低的功耗,将对陆地、海上和海底、空中和太空中的许多应用具有吸引力。

这篇文章没有任何有用的信息。你的调查工作并没有提供任何有用的信息甚至是线索。他们显然会使用更先进的生产节点,但除此之外,你什么都没有。Ie。它可能是基于FLASH的,也可能不是。

此外,你对北极火的真正问题没有任何了解——蹩脚的补丁工具,高昂的价格和陈旧的SERDES。

它们可以达到12gbps,但只能是PCIev2。在PCIE5发布的时候,花这么多美元购买芯片,只是为了通过PCIev2连接到PC上,这似乎是亵渎神明,并将其锁定在如此多的用途之外。

前一段时间有人在论坛上问他们为什么不能做多速SERDES车道,这样一个就可以有一个(到)PCIev5车道,另一个可以到PCIev4车道,另外两个可以到PCIev3车道等等。

通过这种方式,可以使用现代的、快速的PCIe版本(即使很窄),而不会使内部路由过载或超出成本上限(只有一个通道是真正快速的)。

MC回答说类似的事情在计划中。

顺便说一句,对RISC-V核心变化的预测似乎是合理的和有趣的。我希望他们的核心速度更快。600兆赫左右不是很好。

顺便问一下,为什么所有的FPGA制造商都把工艺进步当作自己的事情?

他们要进入更先进的制造工艺,这在默认情况下会带来一定的速度/功率进步。那么,为什么所有这些家伙都花了很大的篇幅来显示流程更改本身带来的加速/功率下降?

如果他们只是简单地说明他们在新流程之外取得了哪些超出预期的改进,这将更容易接受……