你可能还记得,今年早些时候,我们看了一个1晶体管(1T) SRAM位单元.(是的,新的内存似乎最近很流行——我们可能还没有结束。)这个1T细胞还有另一个故事,只不过它与记忆无关。它与我们工具箱中最基本的设备之一有关:晶体管本身。芝诺公司声称,他们可以将ON晶体管的驱动电流提高两倍——这通常需要几个工艺节点才能实现。而且所有这些都不会增加泄漏——这是几个流程节点不太可能提供的。

他们称之为βMOS,“beta”代表“增强”。他们是在描述1T位元时偶然发现的。让我们从检查单元格开始。

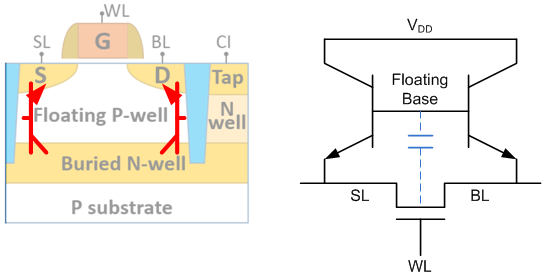

其原理是,在MOS通道下方有一个高电压的埋置n阱,在其上方有一个孤立的浮动p阱,你可以将低MOS晶体管转换成一个更复杂的野兽,包括两个npn双极晶体管,埋置n阱充当集电极。

(左图基于Zeno提供的图片)

通过足够快地提高MOS晶体管的栅极(由字线控制),你耦合到浮动的p阱上,这就形成了双极晶体管的基极。这将使基极泵出,使电流流过集电极,它以一种可以被解释为状态的方式变得自我维持——因此它被用作存储单元。

如果这是你的电池,你自然会改变所有的电压和其他条件来限制它工作的条件。其中一个电压是埋在地下的n井被提升到的水平——换句话说,收集器上的电压范围是什么,可以确保可靠的读写和存储?

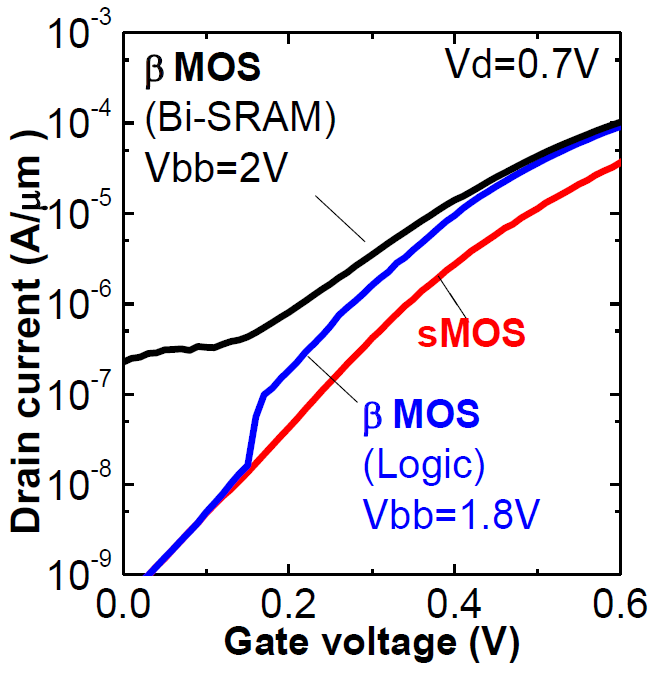

在描述过程中,芝诺发现了一件奇怪的事情。当n阱偏置在2v左右时,比特元的表现符合预期。我们在下一个图中看到这个测试,在那里我们看到I/V曲线。上面的黑线代表1T位单元,它在电压范围的低端和高端都具有高驱动。

一个标准MOS器件(他们称为sMOS),由于双极晶体管没有做出贡献,泄漏电流较低;下面用红色表示。但是,当你把埋在地下的n孔电压拨得更低时,会发生一件有趣的事情:当门电压高时,它就像1T位单元一样,具有额外的驱动电流。但是由于栅极电压较低,它的作用就像sms晶体管一样。事实上,如果你从左到右扫描,他们所谓的βMOS曲线(蓝色)开始重叠在sMOS曲线上,但是,在某一点上,它偏离了这条曲线,并加入了1T曲线。这是怎么回事?

(图片由Zeno提供)

第一件事是不继续的是记忆。在V下面bb限制是(这里,在1.8到2v之间),没有足够的电流来建立内存状态。你得到电流,但它不是自我维持的,所以当栅极电压降低时电流就消失了。

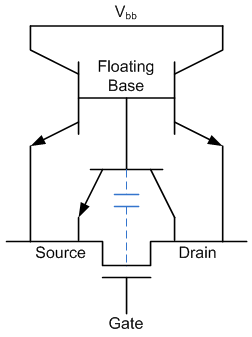

在分析这个问题时,芝诺假设了一个相当复杂的工作机制,它涉及到另一个寄生npn——这次是在源和漏之间,埋在地下的p井作为它的浮动基座(就像它对两个垂直npn所做的那样)。

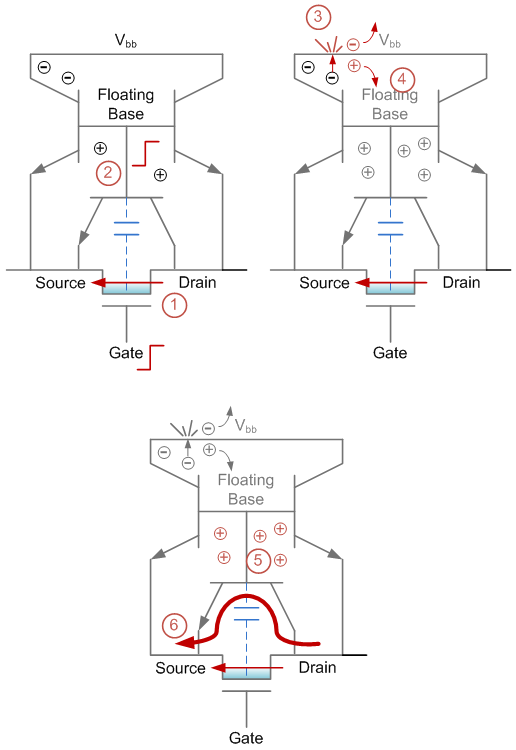

看到这里,你可能会想说,这只是在漏极电压很高时,耦合浮动基打开了横向npn。但这显然没有那么简单,因为你需要某种机制来解释基区中有足够多的洞。以下是他们提出的一系列事件:

- 首先,MOS晶体管打开,在通道中产生反转。

- 接下来(实际上是同时),垂直双极晶体管打开,就像1T位单元一样。这使得电流流过埋在地下的n孔。这意味着电子向上移动到集电极(在上面的晶体管图中,也就是说,在硅图中,它们向下移动到埋在地下的n阱)。

- 当电子击中埋在地下的n阱结时,它们这样做的能量足够引起撞击电离。这就产生了自由电子-空穴对,电子被扫进和扫出收集器,而空穴…

- 转移到基地地区,在那里他们…

- 刺激横向双极晶体管更多地打开。

- 这为电流从漏极到源极提供了第二条路径,绕过正常MOS通道,通过横向npn到达。因此,比正常的驱动器更高。

这里有趣的是额外电流的来源。对于1T位单元,额外的电流来自一个垂直npns的集电极。但在这种情况下,它来自MOS器件的漏极通过横向npn。

当然,他们仍然在描述这种现象,但如果它经受住了审查,那么,嗯,似乎这将是巨大的。他们说,它可以应用于任何使用浅沟的流程节点。他们已经运行了28纳米的平面晶体管,他们还模拟了finfet,以证明这对他们也有帮助。

换句话说,这是一个巨大的飞跃,而不必求助于昂贵的技术,如纳米线或隧道fet或其他花哨的东西。

几乎听起来好得令人难以置信——事实上,我突然想到,这种创新的一个方面很容易被忽视:这是一种AC现象。它依赖于闸门上升速度足够快,能够有效地连接到浮动底座上。

这对于该技术的实施例来说比对于1T细胞来说更重要。如果一个存储单元需要一个特定的、受控的转换速率来工作,那么预期这个需求将被工作到(在本例中)字线驱动程序需求中,并且它将被构建到IP中。但如果你的基本晶体管要利用这种现象,那么每个设计师都可以在任何给定的情况下使用它。

虽然回转率是标准设计中的一个因素,但作为关键速度路径的一部分,它更多的是AC考虑。当考虑到像驱动这样的直流特性时,你必须考虑驱动的转换速率是否足以启动升压驱动,这并不常见。

当然,如果其中一种驱使另一种离你很近,增强驱动力的事实更有可能让你得到你需要的上升速度。但如果你要排长队呢?那些长串末端的晶体管门是否会检测到一个被稀释的上升速率,从而阻止它们实现升压?这将成为设计师和设计工具的新考虑因素吗?

这取决于启动加速功能所需的最低上升速率。如果100ns或1000ns的上升仍然有效,那么这可能远远超出了现实预期的范围,你真的不需要担心。但是如果极限是10ns,会不会太近了?

我向Zeno询问了这个问题,首席执行官Yuniarto Widjaja指出,他们已经使用1v / 100ns的上升速率进行了许多测量。他们也一直在做TCAD模拟,他们仍然在每2毫秒1v的上升速率下看到了增强效应(我再次与他们检查,以确认这确实是ms,而不是µs……换句话说,这些上升时间大约比正常的ns时间尺度慢一百万倍)。特别是最后一个速率比正常的切换速度要慢得多,所以应该把这个问题解决了。

另一件需要注意的事情是,这个功能解决了很大程度上的数字问题。我无法想象这对模拟设计有什么帮助。你将有更多的旋钮来拨号和描述(埋藏的n井偏置电压),并且I/V曲线的控制必须更加精确和可控。

我们在上面看到,本质上,随着电压的上升,I/V曲线从sMOS曲线切换到1T曲线。对于数字设计来说,开关具体发生在哪里并不重要。但是如果你要把它用于模拟,这是一个必须精确控制的新特性。此外,这需要对晶体管门进行震动才能打开升压,我相信一些有创意的模拟巫师会非常努力地找到一种方法来利用它,但这对于日常模拟设计来说听起来不切实际。

与此同时,在数字世界中,如果这一技术能够投入商业使用,它将极大地促进当前的流程节点,使它们能够更长久地保持相关性,并避开昂贵得多的高级节点。

更多信息:

你觉得芝诺的高驱晶体管加速器怎么样?